# Wafer-level Hermetically Sealed Silicon Photonic MEMS

GAEHUN JO,<sup>1</sup> PIERRE EDINGER,<sup>1</sup> SIMON J. BLEIKER,<sup>1</sup> XIAOJING WANG,<sup>1</sup> ALAIN YUJI TAKABAYASHI,<sup>2</sup> HAMED SATTARI,<sup>2</sup> NIELS QUACK,<sup>2</sup> MOISES JEZZINI,<sup>3</sup> JUN SU LEE,<sup>3</sup> PETER VERHEYEN,<sup>4</sup> IMAN ZAND,<sup>5</sup> UMAR KHAN,<sup>5</sup> WIM BOGAERTS,<sup>5</sup> GÖRAN STEMME,<sup>1</sup> KRISTINN B. GYLFASON,<sup>1</sup> FRANK NIKLAUS<sup>1,\*</sup>

Received XX Month XXXX; revised XX Month, XXXX; accepted XX Month XXXX; posted XX Month XXXX (Doc. ID XXXXX); published XX Month XXXX

The emerging fields of silicon (Si) photonic micro-electromechanical systems (MEMS) and optomechanics enable a wide range of novel high-performance photonic devices with ultra-low power consumption, such as integrated optical MEMS phase shifters, tunable couplers, switches, and optomechanical resonators. In contrast to conventional SiO<sub>2</sub>-clad Si photonics, photonic MEMS and optomechanics have suspended and movable parts that need to be protected from environmental influence and contamination during operation. Wafer-level hermetic sealing can be a cost-efficient solution, but Si photonic MEMS that are hermetically sealed inside cavities with optical and electrical feedthroughs have not been demonstrated to date. Here, we demonstrate wafer-level vacuum sealing of Si photonic MEMS inside cavities with ultra-thin caps featuring optical and electrical feedthroughs that connect the photonic MEMS on the inside to optical grating couplers and electrical bond pads on the outside. We used Si photonic MEMS devices built on foundry wafers from the iSiPP50G Si photonics platform of IMEC, Belgium. Vacuum confinement inside the sealed cavities was confirmed by an observed increase of the cut-off frequency of the electro-mechanical response of the encapsulated photonic MEMS phase shifters, due to reduction of air damping. The sealing caps are extremely thin, have a small footprint, and are compatible with subsequent flip-chip bonding onto interposers or printed circuit boards (PCBs). Thus, our approach for sealing of integrated Si photonic MEMS clears a significant hurdle for their application in high-performance Si photonic circuits.

# 1. INTRODUCTION

Over the past decade, photonic integrated circuits (PICs) have evolved rapidly. They have already found widespread use in telecommunication systems, where they serve as highly miniaturized optical transceivers, and are being developed for emerging applications in medical technology and sensing [1]. Especially, silicon (Si) photonics has established itself as a scalable technology that is becoming widely available via commercial foundry platforms [2–5]. Si photonics foundries offer a wide range of devices, such as high-speed modulators and photodetectors, as well as high-quality passive waveguides. Moreover, the availability of Si photonics has catalyzed new research fields that leverage the excellent mechanical properties of Si in combination with its large refractive index. For example, integrated optical sensors based on suspended Si waveguides achieve high

sensitivity, due to the high Si-air refractive index contrast that allows for high mode deconfinement [6–9]. Furthermore, optomechanical coupling and optical forces can be harnessed, for uses such as particle manipulation, telecommunication, or on-chip nonreciprocal transmission [10–12]. Movable and tunable Si photonic microelectromechanical (MEMS) components also show promise as low-power and compact reconfigurable photonic building blocks for large scale programmable photonic circuits that can be reprogrammed for a variety of optical functions [13–19], i.e. generic Field-Programmable Photonic Integrated Circuits (FP-PIC), similar to field-programmable gate arrays (FPGA) in electronics. In contrast to conventional SiO<sub>2</sub>-clad photonic devices, optomechanical, and Si photonic MEMS devices feature suspended and movable parts, and exposed waveguide cores. These devices are much more susceptible to environmental influences such as exposure to dust, gas composition, and humidity levels, and,

<sup>&</sup>lt;sup>1</sup>Division of Micro and Nanosystems, KTH Royal Institute of Technology, 114 28 Stockholm, Sweden

<sup>&</sup>lt;sup>2</sup>École Polytechnique Fédérale de Lausanne (EPFL), 1015 Lausanne, Switzerland

<sup>&</sup>lt;sup>3</sup>Tyndall National Institute, Lee Maltings Complex Dyke Parade, T12 R5CP Cork, Ireland

<sup>&</sup>lt;sup>4</sup>imec vzw. 3DSIP Department, Si Photonics Group, Kapeldreef 75, 3001 Leuven, Belgium

<sup>&</sup>lt;sup>5</sup>Ghent University - IMEC, Photonics Research Group, Department of Information Technology, Technologiepark-Zwijnaarde 126, 9052 Gent, Belgium

<sup>\*</sup>Corresponding author: <a href="mailto:frank.niklaus@eecs.kth.se">frank.niklaus@eecs.kth.se</a>

therefore, require a robust packaging solution to ensure reliable operation over extended time periods. Hermetic sealing in inert gas or vacuum, protecting the photonic MEMS from such environmental influence, is crucial for their reliable performance, and serves as a prerequisite for their commercialization [20–22].

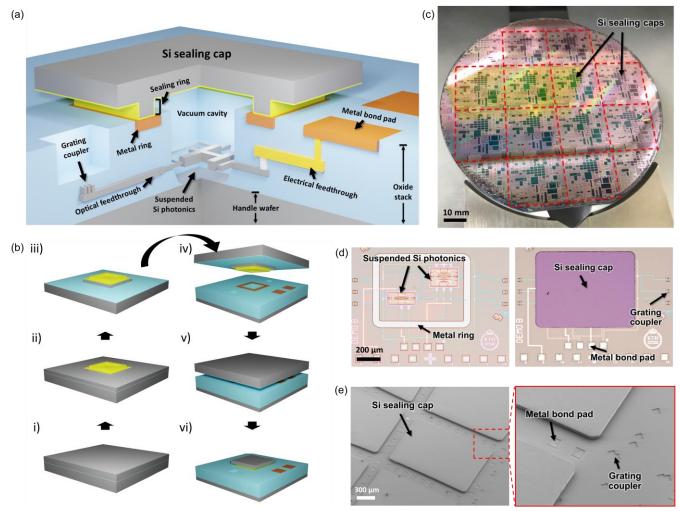

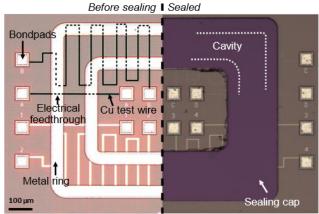

Fig. 1. Wafer-level hermetic packaging of Si photonic MEMS. (a) Cut-away 3D illustration of a hermetically sealed suspended photonic MEMS device. (b) Process flow of the hermetic packaging approach by transfer bonding of a Si sealing cap: Step i-ii) Patterning of sealing rings by deep reactive ion etching (DRIE) on the SOI cap wafer, followed by TiW/Au deposition and etching. iii) Etching of the sealing caps. iv-v) Wafer alignment of the SOI wafer containing the caps and the photonic device wafer, and bonding of the wafers inside a vacuum chamber at 250 °C.vi) Removal of the Si handle (substrate) layer of the SOI cap wafer by DRIE such that only the thin vacuum sealing caps remain on the photonic device wafer. (c) Photograph of a full wafer with sealed Si photonic MEMS. (d) Microscope images before sealing (left), and after sealing (right). (e) SEM images of the bond pads and grating couplers around the thin sealing caps.

There exist mature wafer-level hermetic packaging solutions for traditional MEMS components that have been reported and successfully employed in industry [23–27]. These approaches offer long-term hermeticity and some of them include electrical feedthroughs, which are electrical connections from the MEMS device inside the sealed cavity to the outside. However, none of the traditional MEMS packaging approaches offer optical feedthroughs, which are essential for photonic devices. To the best of our knowledge, wafer-level hermetic sealing of integrated photonic MEMS devices, with incorporated electrical and optical feedthroughs, has not yet been demonstrated. Thus, there is a clear need for a cost-effective hermetic packaging technology that is fully compatible with standard PIC foundry platforms and does not block the optical interfaces of the Si photonics chip [28–33].

In this work, we demonstrate an approach for wafer-level hermetic sealing of Si photonic MEMS inside cavities with electrical and optical feedthroughs. We validate the feasibility of our approach by sealing Si photonic MEMS devices on foundry wafers from the iSiPP50G Si photonics platform of IMEC, Belgium [34,35]. Our sealing approach uses low-temperature (250 °C) Au-Al thermo-compression wafer bonding that is fully compatible with the Si photonic foundry wafers [26]. We demonstrate sealing of a total of 672 individual cavities with caps that are 25  $\mu$ m-thick and of varying dimensions (from 0.45 mm  $\times$  0.33 mm to 2.80 mm  $\times$  2.95 mm), achieving a vacuum sealing yield of 90 %. We experimentally verify the functionality of the sealed photonic MEMS devices and the optical and electrical feedthroughs, and we demonstrate that the vacuum encapsulated photonic devices feature higher mechanical quality factors (Q) and increased mechanical cut-off frequency, due to the elimination of air damping.

# 2. VACUUM SEALING OF SI PHOTONIC MEMS

Our approach to vacuum sealing of Si photonic MEMS on PIC wafers consist of metal-to-metal bonding of thin Si caps on top of cavities

containing the suspended Si photonic MEMS, as illustrated in Fig. 1(a), which shows a cut-away 3D illustration of a single sealed cavity. This vacuum sealing approach is fully compatible with standard Si photonic foundry wafers and their standard metallization layers. In all our experiments, we used 100-mm diameter wafers, for compatibility with our processing tools. The silicon-on-insulator (SOI) based PIC wafers were downsized from 200-mm diameter foundry wafers from the iSiPP50G Si photonics platform of IMEC, Belgium [3,34,36]. The iSiPP50G platform provides an extensive component library, including state-of-the-art optoelectronic modulators and detectors, grating couplers, and a two-level copper-damascene metal interconnect stack with Al/Cu metal bond pads for the back-end electrical connections. To provide access to the photonic MEMS devices, the back-end-of-line (BEOL) oxide stack is locally etched to create open cavities. We then post-processed these cavities using vapor-HF etching to create suspended waveguides and movable MEMS devices, as illustrated in Fig. 1(a). To hermetically encapsulate these devices inside the cavities, we prepared 25 µm-thick Si sealing caps on a separate 100-mm diameter SOI wafer, using contact lithography, dry etching, and metal deposition (Fig. 1(b)i-iii). The resulting Si sealing caps on the SOI wafer consist of a flat lid section with a  $20 \, \mu m$  wide protruding sealing ring covered by a  $2 \,$ μm-thick gold layer (Fig. 1(a) and Fig. 1(b)iii). On the photonic device wafer, corresponding aluminum/copper (Al/Cu) metal rings (orange rings in Fig. 1(a)) were defined in the standard metal bond pad layer of the iSiPP50G process (orange pads in Fig. 1(a)). The sealing of the cavities on the photonic wafer was performed in vacuum using a commercial wafer bonder. In this step, the Au-covered sealing rings on the cap wafer were bonded to the Al/Cu metal rings on the photonic device wafer (Fig. 1(b)iv and v) using thermo-compression bonding with a bond pressure of 400 MPa and a bonding temperature of 250 °C for 45 min. After the bonding, we removed the handle layer of the cap wafer by deep reactive ion etching (DRIE), leaving only the 25 µm-thick Si caps on top of the cavities containing the photonic devices (Fig. 1(b)vi and Fig. 1(a)). A detailed description of the wafer preparation, bonding and cap transfer process is presented in the experimental section. Using this sealing approach, we successfully sealed Si photonic devices on wafer-level as shown in Fig. 1(c), where the sealing caps are visible in a dark green color against the bright background of the iSiPP50G device wafer. A comparison of Si photonic MEMS devices before and after sealing is shown in Fig. 1(d). In the left microscope image, the suspended Si photonic MEMS devices are visible, as well as the Al/Cu metal ring around the cavity, while the right image shows the same devices encapsulated by a Si sealing cap. The image on the right shows the bond pads and grating couplers that are standard designs part of the iSiPP50G platform and that connect to the electrical and optical feedthroughs, which are buried in the BEOL oxide stack [36,37]. These feedthroughs are designed using the foundry metallization layers, and are placed underneath the metal rings, thus connecting the electrical and optical I/O to the vacuum sealed photonic MEMS devices inside the cavity (Fig. 1(a)). Hence, the photonic devices can be easily addressed optically and electrically and characterized even after they have been sealed. Closeups of the bond pads and grating couplers around the sealing caps are shown in the SEM images in Fig. 1(e), which also illustrates the thinness of the 25 µm-thick sealing caps, and the fact that both the optical and electrical interfaces remain accessible.

# 3. OPTICAL AND ELECTRICAL CHARACTERIZATION OF SEALED PHOTONIC DEVICES

Essential requirements on PICs containing vacuum packaged photonic MEMS devices are functional optical and electrical feedthroughs that provide connections between the photonic MEMS inside the packages and the outside world, as well as maintaining the mechanical integrity of the photonic MEMS devices during and after the sealing process. In

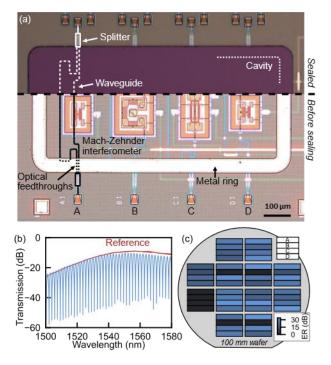

our approach, the optical and electrical feedthroughs travel underneath the metal rings of the photonic device wafer, buried within the BEOL dielectric layers that are part of the photonics foundry platform, thereby ensuring the hermeticity of the package. We evaluated optical feedthroughs that were connected to four different types of sealed Mach-Zehnder Interferometers (MZI) (split image in Fig. 2(a)). The optical feedthroughs used here were standard iSiPP50G strip waveguides with 450 nm width and 220 nm thickness that were buried in the BEOL oxide layer. We optically interfaced all four MZI devices with grating couplers, thereby enabling connection to an external optical fiber-coupled light source and detector. We measured the optical transmission of the devices across all 12 dies on the sealed 100-mm wafer using wavelengths from 1500 to 1580 nm. We found that the maximum transmission follows the reference envelope, without any noticeable impact of the sealing on the optical performance of the waveguides passing below the metal rings (Fig. 2(b)). Furthermore, we assessed the impact of the sealing process on the suspended photonic structures inside the cavities, by comparing the characteristics of the four MZI devices in the cavity. All four MZI devices use a similar test circuit that only differ in the short, suspended waveguide section present in one arm of the interferometer. The suspended waveguide sections differ in length and stiffness, where device A has the most robust design (shorter and straight), and device B the least robust one (longer, multiple anchors and bends). We extracted the Extinction Ratio (ER) of all devices across the 12 dies on the wafer, as indicated in Fig. 2(c). If a suspended waveguide section collapses, the optical losses increase drastically as the light leaks into the Si substrate. As a result, the transmission spectrum of the corresponding interferometer has an  $\ensuremath{\mathsf{ER}}$ of 0. Devices of type A, C, and D all display interference fringes, except for a single die on the edge of the wafer (in total 33 suspended devices out of 36). The waveguide sections in those devices did not collapse, and this confirms that our sealing method is compatible with suspended photonic devices. Measurements of device type B showed a higher collapse count (in total 7 suspended devices out of 12), which may be because device type B has the least robust mechanical design. The most fragile suspended devices tend to collapse due to very low out-of-plane stiffness and stiction during the vapor-HF release step, and it is likely that these devices were already collapsed before the sealing. Overall, the sealing did not lead to a systematic collapse of suspended waveguide sections, which is a key requirement for a viable process for sealing of photonic MEMS devices.

Fig. 2. Optical characterization of sealed Mach-Zehnder interferometers (MZIs) with suspended waveguide sections in one arm. (a) Split view of optical microscope images of four MZI devices before and after sealing within a rectangular cavity. (b) Example of measured optical transmission spectrum, along with the transmission spectrum of a reference grating-tograting structure outside the sealed cavity. (c) Wafer map of the Extinction Ratio (ER) at a wavelength of 1550 nm of the MZI devices placed on dies across the 100-mm wafer. An ER of 0 dB corresponds to collapsed waveguide sections. Four de-vices were measured on each die.

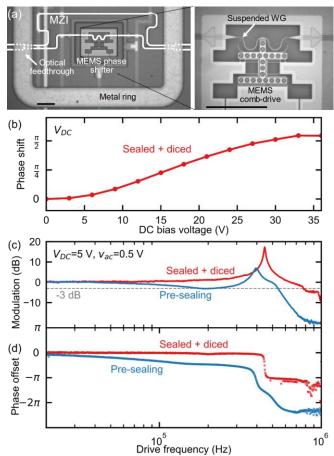

Next, we evaluated the impact of vacuum sealing on the performance of a Si photonic MEMS phase shifter. To read out the phase shift as a function of actuation voltage, the phase shifter is included in one arm of an MZI (Fig. 3(a)). It corresponds to device D in Fig. 2(a). The phase shifter consists of a fixed suspended waveguide near a slender movable Si beam. The Si beam is attached to an in-plane MEMS comb-drive actuator, and when a bias voltage is applied between the movable and fixed electrodes, the effective index of the guided mode in the suspended waveguide is decreased as the narrow Si beam is moved away from it [18]. The change in effective index in the suspended waveguide translates into a phase shift, which we measured after sealing and dicing (Fig. 3(b)). The phase shifter worked as intended after sealing (and dicing), and achieved a  $\pi/2$  phase shift at 36 V DC actuation, which is consistent with the device design. We also measured the mechanical frequency response of the phase shifter using a lock-in amplifier, and compared the result before and after sealing (Fig. 3(c-d)). We applied a DC bias of 5 V to the actuator, with an AC modulation amplitude of 0.5 V. The oscillating phase shift results in a modulation of the MZI output amplitude, which was measured with the lock-in amplifier. We observed a resonance in both cases (396 kHz and 446 kHz, before and after sealing, respectively). Interestingly, the mechanical quality factor of the device improved significantly after sealing, from 8 to 36. Moreover, the amplitude response after sealing was flatter up to the resonance, with a -3dB cut-off frequency increasing from 213 to 776 kHz. We attribute these improvements to a reduction of air damping when the devices operate in vacuum inside the sealed cavity. On-chip vacuum packaging has potential applications for faster photonic MEMS actuators and more sensitive optomechanical devices.

Fig. 3. Effect of vacuum sealing on the performance of an Si photonic MEMS phase shifter. (a) Optical microscope image of the phase shifter before sealing. Inset: Close-up of the suspended waveguide and movable actuator. (b) Phase shifter response in DC up to 36 V at a wavelength of 1550 nm, after sealing and dicing. (c-d) Mechanical frequency response of the device before and after sealing, with (c) the modulated output from the on-chip Mach-Zehnder Interferometer, and (d) the mechanical phase offset with respect to the driving signal.

## 4. CHARACTERIZATION OF VACUUM SEALING CAPS

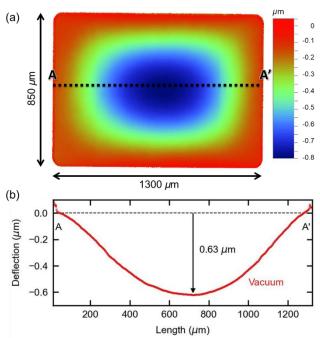

For a wafer-level hermetic sealing process to be viable in practical applications, it must offer acceptable yield. We define here the waferscale bonding yield as the fraction of sealing caps that are successfully transferred and bonded to the photonic device wafer and that seal the cavity without detectable gross leakage. We investigated both the yield of our process and the hermeticity of the sealed cavities, by measuring the deflection of the thin Si caps using an optical profilometer to verify the presence of a vacuum inside the cavity. If a cavity is hermetically sealed, the cap deflects to the inside of the cavity, due to the difference in pressure between the vacuum inside the cavity and the outside atmosphere, as exemplified in the deflection measurement in Fig. 4. While the cap deflection does not provide an accurate measurement of the vacuum level for low gas pressure, we estimated the vacuum pressure inside the sealed cavities to be on the order of a few mbar, based on the results from previous residual gas analysis measurements performed on test cavities that were sealed with the same approach [26]. To estimate the yield and reliability of our sealing process, we characterized a total of 128 sealed cavities distributed across four dies of a sealed Si photonic foundry wafer (all cavities had a side length of 600 µm or larger). To account for processing variations across the wafer, we selected two dies located at the center and two dies

located at the edge of the wafer for this evaluation. We found that of the 128 cavities, 115 were successfully sealed directly after the sealing process, which corresponds to a sealing yield of about 90 %. To investigate possible gross leakage of the sealed cavities, we repeated the cap deflection measurements after storing the sealed wafer for 21 days in ambient atmosphere. We did not observe a measurable change of the cap deflection in any of the cavities (within the ± 60 nm accuracy of our measurement approach), indicating that there was no gross leak in any of the 115 successfully sealed cavities. In contrast, 13 leaked cavities clearly show flat without deflection, indicating no pressure difference inside and outside the cavities. We also evaluated the robustness and process compatibility of the sealed cavities using standard wafer dicing to cut the wafer into separate dies, which is a critically important step in component manufacturing. Therefore, we diced the wafer with the sealed cavities into 12 dies. Again, we found no difference in cap deflection in any of the 115 sealed cavities after dicing, demonstrating the robustness and resilience of the sealed cavities to standard wafer dicing.

Fig. 4. White-light interferometry measurement of the deflection of a Si sealing cap. (a) Top view heatmap showing the deflection of a 25  $\mu$ m-thick Si cap with an area of 850  $\mu$ m × 1300  $\mu$ m, resulting from the pressure difference between the inside and outside of the sealed cavity. (b) A cross-section of (a) shows a maximum cap deflection of 0.63  $\mu$ m at the center of the Si cap.

# 5. COMPATIBILITY WITH HIGH-DENSITY CHIP INTEGRATION

Due to the ultra-thin caps and the compact footprint, our vacuum sealing approach is exceptionally well suited for high density photonic system integration. Reducing the overall device volume facilitates a higher integration density and thus smaller and more powerful PIC-based components. First, an important contributing factor to the small footprint that we can achieve with our sealing approach is the narrow sealing rings that we employ in the caps. The total width of the sealing rings in this work is only 20  $\mu m$ , thereby enabling a high integration density which reduces costs and improves performance due to shorter optical and electrical signal paths. The narrow sealing rings also provide

the benefit of great flexibility in the sealing cap design. The caps can be designed to seal not only one device in a single cavity, but multiple devices in one or several cavities using one single cap (Fig. 1d and Fig. 2a). This flexibility also allows for different shapes of sealing caps to be manufactured in the same process. Possible shapes include square, rectangular (Fig. 1d and Fig 2a), triangular, L-shaped, and can even include open regions for additional routing options. As a demonstration of the latter, we designed a donut-shaped cap where a second inner metal ring is used to ensure hermeticity, which allows for electrical probing through the opening in the center of the sealing cap, as shown in Fig. 5. To verify the electrical integrity of these feedthroughs, we included eight different metal wires featuring varying lengths, width, and number of sealing ring transitions. We measured resistances between 5 and 50  $\Omega$  for all eight electrical feedthrough designs both before and after the sealing process, with no observable difference in resistance to that of identical metal lines in reference devices without sealing caps. The measured resistance values comply with the related specifications of the iSiPP50G platform.

Fig. 5. Donut-shaped sealed cavity with 8 different electrical feed-through test structures. The feedthroughs pass below the metal rings and connect a bond pad outside the cap with a bond pad in the center of the donut. Left: optical microscope image before sealing. Right: after sealing.

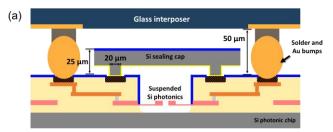

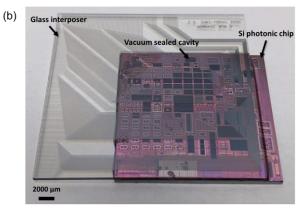

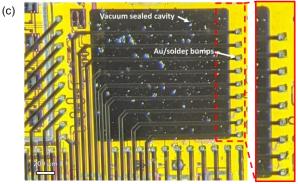

Additionally, as the sealing caps in our approach are thinner (25 µmthick, including the protruding sealing rings) than the height of typical flip-chip Au/solder bumps (about 50 µm), the caps fit neatly between the bumps and, thus, enable face-to-face flip-chip bonding with high I/O counts of the packaged photonic devices, as illustrated in Fig. 6(a). To demonstrate the vertical chip integration capability of our packaged Si photonic devices, we flip-chip bonded a chip containing hermetically sealed photonic MEMS phase shifters to a glass interposer using gold stud bumping. The interface between the glass interposer and the photonic chip consisted of 599 gold stud bumps (219 functional electrical connections and 380 mechanical bumps) that were bonded to predefined bond pads ( $50 \, \mu m \times 50 \, \mu m$ ) on the photonic chip. We did not observe any defects in the flip-chip bonded photonic chip when visually inspecting it through the glass interposer (Fig. 6(b-c)). These results demonstrate that the sealed photonic devices with thin sealing caps can be placed in between the Au/solder bumps (Fig. 6(c)), thus indicating that our photonic device packaging approach is compatible with largescale flip-chip integration of photonic chips, featuring a high number of I/O connections to the sealed photonic devices in a small footprint.

Fig. 6. Demonstration of flip-chip bonding of a chip with sealed photonic devices to a glass interposer. (a) Schematic cross-section of a packaged Si photonic chip that is flip-chip bonded to a glass interposer. (b) Photograph of a packaged Si photonic chip that is flip-chip bonded to a glass interposer. (c) Photograph of the caps on top of the vacuum sealed cavities and Au/solder bumps which are visible through the glass interposer.

# 6. CONCLUSIONS

We have presented the first wafer-level hermetic sealing solution for Si photonic MEMS that is compatible with Si photonic foundry wafers and offers ultra-thin wafer-level packages featuring optical and electrical feedthroughs. Our sealing process employs Au-to-Al thermocompression wafer bonding at a temperature of 250 °C, which is fully compatible with standard IC and photonic foundry wafers. We have demonstrated hermetic sealing of Si photonic MEMS on a photonics foundry wafer from IMEC (iSiPP50G Si photonics platform), with a sealing yield of approximately 90 %. We demonstrated functional optical and electrical feedthroughs that connect to photonic devices inside sealed cavities. Moreover, we showed improved mechanical response of a photonic MEMS phase shifter that was packaged in a vacuum. The photonic packages presented here display a small and flexible footprint and offer full compatibility with subsequent flip-chip bonding with large I/O counts for high-density packaging of photonic circuits. We believe that our wafer-level hermetic sealing approach is a very promising and versatile solution for novel integrated photonics

applications, such as low-power photonic MEMS-based circuits and onchip integrated optomechanics.

## **EXPERIMENTAL SECTION**

#### A. Device wafer fabrication

The device wafer was fabricated in the standard iSiPP50G Si photonic foundry platform of IMEC, Belgium. This technology platform offers a vast range of active and passive components, such as high-speed optoelectronic modulators and photodetectors as well as high-quality passive waveguides After receiving the processed Si photonic wafers from the foundry, they were downsized from a diameter of 200-mm down to a diameter of 100-mm, for compatibility with our 100-mm diameter fabrication tools. To create suspended photonic devices, an additional post-processing step was employed on the foundry wafers. Therefore, a hydrofluoric acid vapor-HF etching step was used to selectively remove the oxide underneath the Si waveguide and device layer, thereby realizing suspended Si photonic devices [13,35]. During this step, a thin alumina (AlO<sub>x</sub>) layer was used to protect the areas of the Si waveguide and device layer that were not to be under-etched [18].

# B. Cap wafer fabrication

A 100-mm diameter SOI wafer with a 25 µm-thick Si device layer, a 1 µm-thick buried SiO2 (BOX) layer, and a 300 µm-thick Si handle layer was used as a donor wafer for the caps. Si sealing caps with dimensions ranging from 450 µm  $\times$  330 µm up to 2812 µm  $\times$  2945 µm were designed. First, the 5 µm high and 20 µm wide sealing rings were formed on the device layer by photolithography and Si deep reactive ion etching (DRIE). Then, a 100 nm-thick TiW and a 2.1 µm-thick Au layer were sputter deposited on the caps and the sealing rings. Thereafter, the Au and TiW layers were selectively etched in  $\rm l_2/KI$  and  $\rm NH_3 \cdot H_2O/H_2O_2$  solutions using a photoresist mask. Finally, the 25 µm-thick caps with the protruding sealing rings were defined by DRIE.

# C. Cap wafer bonding and transfer of caps

The SOI wafer containing the caps was bonded to the Si photonic foundry wafer containing the photonic MEMS devices using Al-Au thermo-compression bonding. Therefore, the two wafers were aligned and clamped together on a bond fixture using a bond aligner tool (Suss BA8, Suss MicroTec AG, Germany), and transferred to a wafer bonder (Suss CB8, Suss MicroTec AG, Germany). First, the chamber of the bonder was evacuated to a pressure of  $< 7 \times 10^{-5}$  mbar and the wafers were then held in the vacuum at a temperature of 50 °C for 60 min. The purpose of this holding step before the wafer bonding is to release parts of the gas molecules that are absorbed in the wafer surfaces and thereby reducing the resulting gas pressure inside the sealed cavities. The use of longer degassing steps and higher degassing temperatures may further improve the resulting vacuum level inside the sealed cavities. Next, the wafers were joined inside the bond chamber and the bond chuck was used to apply a bonding force of 28 kN to the wafer stack. For the total area of all the sealing rings present on the 100-mm diameter wafers of 4.85 mm<sup>2</sup>, this resulted in a bond pressure at the bond interfaces of approximately 400 MPa. While applying the bond force, the temperatures of the top and bottom bond chucks were ramped to 250 °Cusing ramping times of 45 min (up) and 45 min (down), respectively, and a holding time of 45 min. After the chuck temperature reached 50 °C, the bond force was released and the bonded wafer stack unloaded from the bond chamber. Finally, the Si handle layer of the SOI cap wafer was removed by DRIE, leaving the singulated Si caps bonded on top of the Si photonic device wafer and encapsulating a vacuum inside the sealed cavities.

#### D. Optical and electrical measurements

The device transmissions, as indicated in Fig. 2, were measured using a Tunable Laser Source and Wavelength Domain Component Analyzer from Agilent (81680A, 86082A). On each chip of the 100-mm diameter wafer with the sealed photonic devices, four sealed MZIs and a nonsealed reference waveguide were characterized. We used PDK building blocks for all passive components in the circuit: grating coupler FGCCTE\_FCWFC1DC\_630\_378, waveguide SWGCTE\_WG\_450, and multi-mode interferometer M12CTE\_FC\_5000\_25400. For all passive measurements, we used a power of  $50 \mu W$ , and the entire wavelength range of the tunable laser source, 1460 to 1580 nm. For the phase shifter response measurement (Fig. 3(b)), we added a DC supply to the setup (Keithley, 2200-72-1). The frequency response of the MEMS phase shifter presented in Fig. 3(c-d) was obtained using a lock-in amplifier from Zurich Instruments (HF2LI). In that case, the tunable laser source was set to 1550 nm, with a power of 4 mW. An external detector (Thorlabs, DET01CFC) was used for measuring the output, directly connected to the lock-in amplifier. For both passive and active measurements, we optimized the input polarization using a polarization controller from Thorlabs (FPC031). The DC and AC measurements were performed on different copies of the device shown in Fig. 3(a), each copy being on a different die.

### E. Characterization of sealing yield

The sealing yield is defined here as the fraction of all cavities that were successfully sealed with a cap and that contained vacuum inside the cavity. Successful bonding of the caps was evaluated by optical inspection and the presence of a vacuum inside the sealed cavities was verified by measuring the deflection the thin caps to the in-side of the cavity using white-light interferometry (Wyko NT9300, Veeco Inc., US). The deflection measurements were repeated after storing the packages for 21 days in ambient atmosphere. Evaluating the cavity sealing by deflection measurements was feasible for caps that are 600 µm x 600 µm or larger in size. For smaller caps, the force exerted by the pressure difference is too small to result in a deflection that provides a reliable measurement of the sealed vacuum. Thus, deflection measurements could not be used to characterize the hermeticity of the smaller packages. Since we observed improvements of the mechanical quality factor of sealed photonic MEMS devices inside these small cavities due to the elimination of air damping, it is likely that most of the small cavities on our wafer were successfully vacuum-sealed. For evaluating if the packages with the Si photonic devices can survive dicing, the 100mm diameter wafer with the sealed cavities was diced into individual chips using a standard dicing saw (DAD 320, Disco Corp., Japan).

# F. Glass interposer fabrication

Fabrication of the interposers begins with sputtering of a Cr-Au-Ti stack, with respective thicknesses of 15 nm, 150 nm, and 10 nm, on a 100 mm float-glass substrate. A direct-laser writing lithography step and subsequent ion beam etch (IBE) patterns the metal traces and contact/bond pads. Next, the whole wafer is covered with a 400 nm-thick sputtered oxide and openings over the contact/bond pads are created by another lithography step and a wet etch with BHF and 1 % HF. The final step is to dice the wafer into individual interposers.

**Funding.** This work has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No.780283 (MORPHIC), as well as from the European Union's Horizon 2020 research and innovation programme under grant agreement No.871740 (ZeroAMP). This work has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement

No.825272 (ULISSES), as well as from the European Union's Horizon 2020 research and innovation programme under grant agreement No.101017186 (AEOLUS).

**Acknowledgments.** We thank Dr. Max Yan for access to measurement equipment, and Mikael Bergqvist and Cecilia Aronsson for assistance with setups.

**Disclosures.** The authors declare that there are no conflicts of interest related to this article.

#### References

- R. Soref, "The Past, Present, and Future of Silicon Photonics," IEEE Journal of Selected Topics in Quantum Electronics 12, 1678–1687 (2006).

- A. Rahim, T. Spuesens, R. Baets, and W. Bogaerts, "Open-Access Silicon Photonics: Current Status and Emerging Initiatives," Proceedings of the IEEE 106, 2313–2330 (2018).

- M. Pantouvaki, P. D. Heyn, M. Rakowski, P. Verheyen, B. Snyder, S. A. Srinivasan, H. Chen, J. D. Coster, G. Lepage, P. Absil, and J. V. Campenhout, "50Gb/s Silicon Photonics Platform for Short-Reach Optical Interconnects," in *Optical Fiber Communication Conference (2016), Paper Th4H.4* (Optical Society of America, 2016), p. Th4H.4.

- A. E. Lim, J. Song, Q. Fang, C. Li, X. Tu, N. Duan, K. K. Chen, R. P. Tern, and T. Liow, "Review of Silicon Photonics Foundry Efforts," IEEE Journal of Selected Topics in Quantum Electronics 20, 405–416 (2014).

- K. Giewont, K. Nummy, F. A. Anderson, J. Ayala, T. Barwicz, Y. Bian, K. K. Dezfulian, D. M. Gill, T. Houghton, S. Hu, B. Peng, M. Rakowski, S. Rauch, J. C. Rosenberg, A. Sahin, I. Stobert, and A. Stricker, "300mm Monolithic Silicon Photonics Foundry Technology," IEEE Journal of Selected Topics in Quantum Electronics 25, 1–11 (2019).

- F. Ottonello-Briano, C. Errando-Herranz, H. Rödjegård, H. Martin, H. Sohlström, and K. B. Gylfason, "Carbon dioxide absorption spectroscopy with a mid-infrared silicon photonic waveguide," Opt. Lett., OL 45, 109–112 (2020).

- Y. Gao, P. Dong, Y. Shi, and Y. Shi, "Suspended slotted photonic crystal cavities for high-sensitivity refractive index sensing," Opt. Express, OE 28, 12272–12278 (2020).

- 8. De. Vos K., I. Bartolozzi, E. Schacht, P. Bienstman, and R. Baets, "Silicon-on-Insulator microring resonator for sensitive and label-free biosensing," Opt. Express, OE 15, 7610–7615 (2007).

- A. L. Washburn and R. C. Bailey, "Photonics-on-a-chip: recent advances in integrated waveguides as enabling detection elements for real-world, lab-on-a-chip biosensing applications," Analyst 136, 227–236 (2010).

- L. Ren, X. Xu, S. Zhu, L. Shi, and X. Zhang, "Experimental Realization of on-Chip Nonreciprocal Transmission by Using the Mechanical Kerr Effect," ACS Photonics 7, 2995

–3002 (2020).

- L. K. Chin, Y. Shi, and A.-Q. Liu, "Optical Forces in Silicon Nanophotonics and Optomechanical Systems: Science and Applications," Advanced Devices & Instrumentation 2020, (2020).

- 12. M. W. Pruessner, D. Park, T. H. Stievater, D. A. Kozak, and W. S. Rabinovich, "Optomechanical Cavities for All-Optical Photothermal Sensing," ACS Photonics 5, 3214–3221 (2018).

- 13. W. Bogaerts, H. Sattari, P. Edinger, A. Y. Takabayashi, I. Zand, X. Wang, A. Ribeiro, M. Jezzini, C. Errando-Herranz, G. Talli, K. Saurav, M. G. Porcel, P. Verheyen, B. Abasahl, F. Niklaus, N. Quack, K. B. Gylfason, P. O'Brien, and U. Khan, "MORPHIC: programmable photonic circuits enabled by silicon photonic MEMS," in Silicon

- *Photonics XV* (International Society for Optics and Photonics, 2020), Vol. 11285, p. 1128503.

- 14. S. Han, J. Beguelin, L. Ochikubo, J. Jacobs, T. J. Seok, K. Yu, N. Quack, C.-K. Kim, R. S. Muller, and M. C. Wu, "32 × 32 silicon photonic MEMS switch with gap-adjustable directional couplers fabricated in commercial CMOS foundry," JOM 1, 024003 (2021).

- T. Nagai and K. Hane, "Silicon photonic microelectromechanical switch using lateral adiabatic waveguide couplers," Opt. Express, OE 26, 33906–33917 (2018).

- C. Errando-Herranz, A. Y. Takabayashi, P. Edinger, H. Sattari, K. B. Gylfason, and N. Quack, "MEMS for Photonic Integrated Circuits," IEEE Journal of Selected Topics in Quantum Electronics 26, 1–16 (2020).

- H. Sattari, A. Y. Takabayashi, P. Edinger, P. Verheyen, K. B. Gylfason, W. Bogaerts, and N. Quack, "Low-Voltage Silicon Photonic MEMS Switch with Vertical Actuation," in 2021 IEEE 34th International Conference on Micro Electro Mechanical Systems (MEMS) (2021), pp. 298–301.

- P. Edinger, A. Y. Takabayashi, C. Errando-Herranz, U. Khan, H. Sattari, P. Verheyen, W. Bogaerts, N. Quack, and K. B. Gylfason, "Silicon photonic microelectromechanical phase shifters for scalable programmable photonics," Opt. Lett., OL 46, 5671–5674 (2021).

- D. Y. Kim, Y. J. Park, D. U. Kim, M. S. Hong, A. Y. Takabayashi, Y. Jeong, J. Park, S. Han, N. Quack, K. Yu, and S. Han, "16-Core Recirculating Programmable Si Photonic MEMS," in *Conference on Lasers and Electro-Optics (2021), Paper STh1Q.6* (Optical Society of America, 2021), p. STh1Q.6.

- K. Gilleo, "Photonics challenge to electronic packaging," IEEE Transactions on Components and Packaging Technologies 24, 309–311 (2001).

- Chinmoy Saha, Daming Zhang, and Sheng Li, "Simulating optoelectronics/MEMS hermetic packaging process with finite element method," in *Fifth International Conference OnElectronic Packaging Technology Proceedings*, 2003. ICEPT2003. (2003), pp. 502–511.

- 22. H. Xia, M. N. Akram, E. Bardalen, A. Roy, K. E. Aasmundtveit, and P. Ohlckers, "Evaluation of Silicon Diaphragms for Hermetic Packaging of Microbolometer Arrays," in 2020 IEEE 8th Electronics System-Integration Technology Conference (ESTC) (2020), pp. 1–5.

- 23. F. Forsberg, A. Lapadatu, G. Kittilsland, S. Martinsen, N. Roxhed, A. C. Fischer, G. Stemme, B. Samel, P. Ericsson, N. Høivik, T. Bakke, M. Bring, T. Kvisterøy, A. Rør, and F. Niklaus, "CMOS-Integrated Si/SiGe Quantum-Well Infrared Microbolometer Focal Plane Arrays Manufactured With Very Large-Scale Heterogeneous 3-D Integration," IEEE Journal of Selected Topics in Quantum Electronics 21, 30–40 (2015).

- 24. T. Tekin, "Review of Packaging of Optoelectronic, Photonic, and MEMS Components," IEEE J. Select. Topics Quantum Electron. 17, 704–719 (2011).

- 25. A. Hilton and D. S. Temple, "Wafer-Level Vacuum Packaging of Smart Sensors," Sensors 16, 1819 (2016).

- X. Wang, S. J. Bleiker, P. Edinger, C. Errando-Herranz, N. Roxhed, G. Stemme, K. B. Gylfason, and F. Niklaus, "Wafer-Level Vacuum Sealing by Transfer Bonding of Silicon Caps for Small Footprint and Ultra-Thin MEMS Packages," Journal of Microelectromechanical Systems 28, 460–471 (2019).

- 27. S.-H. Lee, J. Mitchell, W. Welch, S. Lee, and K. Najafi, "Wafer-level vacuum/hermetic packaging technologies for MEMS," in R. C. Kullberg and R. Ramesham, eds. (2010), p. 759205.

- N. Pavarelli, J. S. Lee, M. Rensing, C. Scarcella, S. Zhou, P. Ossieur, and P. A. O'Brien, "Optical and Electronic Packaging Processes for Silicon Photonic Systems," Journal of Lightwave Technology 33, 991–997 (2015).

- L. Zimmermann, G. B. Preve, T. Tekin, T. Rosin, and K. Landles, "Packaging and Assembly for Integrated Photonics—A Review of the ePIXpack Photonics Packaging Platform," IEEE Journal of Selected Topics in Quantum Electronics 17, 645–651 (2011).

- K. Najafi, "Micropackaging technologies for integrated microsystems: applications to MEMS and MOEMS," in Micromachining and Microfabrication Process Technology VIII (International Society for Optics and Photonics, 2003), Vol. 4979, pp. 1–19.

- 31. P. D. John H. Lau, *3D IC Integration and Packaging* (McGraw-Hill Education, 2016).

- K. Zoschke, P. Mackowiak, K. Kröhnert, H. Oppermann, N. Jürgensen, M. Wietstruck, A. Göritz, S. Tolunay Wipf, M. Kaynak, and K.-D. Lang, "Cap Fabrication and Transfer Bonding Technology for Hermetic and Quasi Hermetic Wafer Level MEMS Packaging," in 2020 IEEE 70th Electronic Components and Technology Conference (ECTC) (2020), pp. 432–438.

- G. Jo, P. Edinger, S. J. Bleiker, X. Wang, A. Y. Takabayashi, H. Sattari, N. Quack, M. Jezzini, P. Verheyen, G. Stemme, W. Bogaerts, K. B. Gylfason, and F. Niklaus, "Wafer-level vacuum sealing for packaging of silicon photonic MEMS," in *Silicon Photonics XVI* (International Society for Optics and Photonics, 2021), Vol. 11691, p. 116910E.

- 34. M. Pantouvaki, S. A. Srinivasan, Y. Ban, P. D. Heyn, P. Verheyen, G. Lepage, H. Chen, J. D. Coster, N. Golshani, S. Balakrishnan, P. Absil, and J. V. Campenhout, "Active Components for 50 Gb/s NRZ-OOK Optical Interconnects in a Silicon Photonics Platform," Journal of Lightwave Technology 35, 631–638 (2017).

- N. Quack, H. Sattari, A. Y. Takabayashi, Y. Zhang, P. Verheyen, W. Bogaerts, P. Edinger, C. Errando-Herranz, and K. B. Gylfason, "MEMS-Enabled Silicon Photonic Integrated Devices and Circuits," IEEE Journal of Quantum Electronics 56, 1–10 (2020).

- P. P. Absil, P. D. Heyn, H. Chen, P. Verheyen, G. Lepage, M. Pantouvaki, J. D. Coster, A. Khanna, Y. Drissi, D. V. Thourhout, and J. V. Campenhout, "Imec iSiPP25G silicon photonics: a robust CMOS-based photonics technology platform," in *Silicon Photonics X* (International Society for Optics and Photonics, 2015), Vol. 9367, p. 93670V.

- D. Vermeulen, S. Selvaraja, P. Verheyen, G. Lepage, W. Bogaerts, P. Absil, D. V. Thourhout, and G. Roelkens, "High-efficiency fiberto-chip grating couplers realized using an advanced CMOScompatible Silicon-On-Insulator platform," Opt. Express, OE 18, 18278–18283 (2010).