Onderbemonsterende technieken met laag vermogen voor een volledig gedigitaliseerde klok-en-data-extractie in multigigabit passieve optische netwerken

Low-Power Subsampling All-Digital Clock and Data Recovery Techniques for Multi-Gigabit Passive Optical Networks

Marijn Verbeke

Promotoren: prof. dr. ir. G. Torfs, prof. dr. ir. P. Rombouts Proefschrift ingediend tot het behalen van de graad van Doctor in de ingenieurswetenschappen: elektrotechniek

UNIVERSITEIT GENT Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. B. Dhoedt Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2017 - 2018

ISBN 978-94-6355-088-8 NUR 959 Wettelijk depot: D/2018/10.500/6

# , FACULTY OF ENGINEERING

Ghent University Faculty of Engineering and Architecture

Department of Information Technology iGent Tower, Tech Lane Ghent Science Park 15, B-9052 Ghent, Belgium

Tel.: +32 9 264 33 40

#### Low-Power Subsampling All-Digital Clock and Data Recovery Techniques for Multi-Gigabit Passive Optical Networks

Marijn Verbeke

#### Members of the examination board:

| Ghent University           |

|----------------------------|

| Ghent University           |

| KU Leuven                  |

| Vrije Universiteit Brussel |

|                            |

Dissertation submitted to obtain the degree of Doctor of Electrical Engineering Academic year 2017-2018

This work was supported by The Agency for Innovation by Science and Technology in Flanders (IWT).

#### Dankwoord

Beste vrienden en familie, Beste collega's en professoren,

Na vier jaar doctoreren, sta ik hier nu met mijn "boek" in mijn handen. Wanneer ik terugblik op die vier jaar, kan ik alleen maar zeggen dat de tijd razendsnel voorbij is gevlogen. Dit komt dankzij mijn toffe collega's en de geweldige sfeer die er heerst in het 'design'-labo, waar ik mijn onderzoek heb gedaan. In het bijzonder wil ik Michael, *Manolo*, Haolin, Joris, Hannes en *Hubert* bedanken voor de vele gezellige koffie-/chocomelkpauzes. Ik denk nu al met heimwee terug aan de lekkere worstenbroodjes (en ander gezond eten), spelletjes- en filmavonden en natuurlijk het zotte vrijgezellenweekend.

De hoofdreden waarom ik besloot om te doctoreren, is omdat ik in de eerste plaats mijn kennis over elektronica en chipontwerp wou uitbreiden. Dankzij de professionele begeleiding van mijn promotoren Guy en Pieter, heb ik het gevoel dat ik die doelstelling meer dan bereikt hebt. Onze wekelijkse meetings – waarbij naast de technische aspecten ook even tijd was voor small talk en andere interessante levenslessen – en de mogelijkheid dat ik altijd kon binnenspringen, wanneer ik ergens vast zat, waren hierbij onmisbaar. De interne reviewprocessen voor publicaties waren bovendien zeer grondig en intensief, maar het resultaat loonde. Bijgevolg, heb ik dan ook het gevoel dat ik het winnende lot heb getrokken met jullie als mijn promotoren.

Ik wil graag ook Johan en Scott bedanken om mij bij de INTEC design groep te laten beginnen, voor de leiding van het labo en de aangeboden hulp. Ook de oude vakgroepvoorzitter em. prof. dr. ir. Daniël De Zutter en de nieuwe vakgroepvoorzitter prof. dr. ir. Bart Dhoedt wens ik te bedanken voor de aangeboden faciliteiten en voor de verzorgde omkadering die voorzien werd in de vakgroep. Hierbij wil ik ook Arno bedanken om steeds zijn kennis en ervaring over *clock and data recovery* en digitaal ontwerp met mij te delen. Jean, bedankt voor de nodige technische ondersteuning en Mike voor de onmisbare administratieve hulp.

Naast het 'harde' werk is natuurlijk ook veel te beleven en ik ben dan ook gelukkig om dit met een fantastische vriendkring te delen. Aan mijn vrienden van het middelbaar Bert, Bruno, Eva, Jochen, Jonas, Stefanie en Ward, dank jullie om ondertussen al meer dan 10 jaar deel uit te maken van mijn leven. Frederick, Lien, Michiel, dank jullie voor de maandelijkse gezellige rendez-vous. Mijn vrienden van de elektrotechniek Dries, Michaël, Sander, Stan, Bernard, Jens, Jeroen, Matthias, Thibault, Tim en Willeke, wens ik graag te bedanken voor de vele leuke en grappige momenten tijdens onze drukke studietijd aan de universiteit. Ondanks onze drukke agenda's, proberen we nog steeds contact te houden met elkaar. En dankjewel aan de Boombalvrienden, met in het bijzonder Ester, David, Mieke en Martijn, voor het vele dansplezier en het gezellig samenzijn.

Uiteraard wil ik graag mijn ouders en mijn zus bedanken. Papa, bedankt om mij te leren klussen en mij steeds met mijn beide voeten op de grond te houden. Mama, dank je voor al je liefde, zorg en ingebouwd stemmetje dat alarm slaat bij enige mogelijke dreiging. Bedankt dat jullie er altijd voor mij zijn en voor alles dat jullie voor mij doen en gedaan hebben. Ik weet dat ik voor goed advies steeds bij jullie terecht kan. Graag wil ik ook mijn geduchte tegenstander in karate en in het opnoemen van filmquotes bedanken en die ik met veel trots mijn zus mag noemen. Dankjewel Eef voor alle gezellige studie-uren aan de keukentafel en zoveel meer.

Het laatste bedankje gaat naar mijn lieve vriendin Jolien. Op het moment dat we nog maar net samen waren, was mijn meest stressvolle tape-out dichtbij. Dank je om toen reeds te tonen dat ik op jouw steun kon rekenen en mij te motiveren om door te gaan. Bedankt om steeds mijn out-of-bed look op punt te stellen wanneer ik naar het werk vertrek en ook om me steeds naar huis te lokken met je lekkere kookkunsten. Ik vind het nog steeds ongelooflijk dat iemand die toch 'een beetje' chaotisch is, zo een grote houvast kan zijn in mijn leven.

Gent, Januari 2018

Marijn Verbeke

# Table of Contents

| Dankwoord                     | ix     |

|-------------------------------|--------|

| Nederlandstalige Samenvatting | xxix   |

| English Summary               | xxxiii |

| List of Publications          | xxxvii |

| Ι | Intr | oduction to Internet Communication and CDRs           | 1  |

|---|------|-------------------------------------------------------|----|

| 1 | Intr | oduction                                              | 3  |

|   | 1.1  | Evolution of Data Consumption                         | 3  |

|   |      | 1.1.1 Internet Traffic                                | 3  |

|   |      | 1.1.2 Power Consumption                               | 7  |

|   | 1.2  | Networks Today                                        | 8  |

|   |      | 1.2.1 Optical Access Networks                         | 9  |

|   |      | 1.2.2 Passive Optical Network                         | 10 |

|   |      | 1.2.3 Optical Receiver                                | 14 |

|   | 1.3  | Objective of this Work                                | 15 |

|   | 1.4  | Overview of the Dissertation                          | 16 |

| 2 | Mul  | ti-Gigabit Clock and Data Recovery                    | 21 |

|   | 2.1  | Introduction to CDRs                                  | 21 |

|   | 2.2  | Jitter and Wander                                     | 23 |

|   |      | 2.2.1 Jitter Specifications                           | 24 |

|   | 2.3  | CDR Types                                             | 27 |

|   |      | 2.3.1 Oversampling without Feedback Phase Tracking .  | 27 |

|   |      | 2.3.2 Phase Alignment without Feedback Phase Tracking | 28 |

|   |      | 2.3.3 Feedback Phase Tracking                         | 29 |

|   | 2.4  | PLL-Based CDR Structure                               | 30 |

|   | 2.5  | Evolut   | ion to Digital CDR                                 | 32 |

|---|------|----------|----------------------------------------------------|----|

|   |      | 2.5.1    | All-Digital CDR Structure                          | 32 |

|   |      | 2.5.2    | Advantages                                         | 33 |

|   |      | 2.5.3    | Challenges                                         | 35 |

|   | 2.6  | Next-O   | Generation (All-Digital) Clock and Data Recovery . | 37 |

|   |      |          |                                                    |    |

| Π | An   | alysis,  | Design and Implementation                          | 45 |

| 3 | Cloc | k and I  | Data Recovery Analysis                             | 47 |

|   | 3.1  | CDR F    | Phase Domain Model                                 | 47 |

|   | 3.2  | Descri   | bing Functions: Pseudo-Linear Model                | 51 |

|   |      | 3.2.1    | Random-Input Describing Function                   | 51 |

|   |      | 3.2.2    | Limit Cycles                                       | 53 |

|   |      | 3.2.3    | Gaussian-plus-Sinusoid-Input Describing Function   | 54 |

|   | 3.3  | Stabili  | ty in Charge Pump CDRs                             | 56 |

|   |      | 3.3.1    | System Relations                                   | 57 |

|   |      | 3.3.2    | Algorithm                                          | 59 |

|   |      | 3.3.3    | Application of the Algorithm                       | 60 |

|   |      | 3.3.4    | Simulation Results                                 | 61 |

|   |      | 3.3.5    | Influence of the CDR Design Parameters             | 64 |

|   |      | 3.3.6    | Further Analytical Approximations                  | 68 |

|   | 3.4  | Jitter A | Analysis in Charge Pump CDRs                       | 71 |

|   |      | 3.4.1    | Jitter Transfer and Jitter Generation              | 72 |

|   |      | 3.4.2    | Jitter Tolerance                                   | 73 |

|   | 3.5  | AD-Cl    | DR Phase Domain Jitter Analysis                    | 76 |

|   |      | 3.5.1    | Sampled-Data Mixed-Signal AD-CDR Model             | 76 |

|   |      | 3.5.2    | Aliasing                                           | 77 |

|   |      | 3.5.3    | Discrete-Time Multi-Rate Modeling of AD-CDR .      | 79 |

|   |      | 3.5.4    | LTV Analysis of Subsampled AD-CDR                  | 82 |

|   | 3.6  | CID in   | Subsampled AD-CDR                                  | 83 |

|   |      | 3.6.1    | Idle Time                                          | 83 |

|   |      | 3.6.2    | Phase Drift                                        | 85 |

|   | 3.7  | Simula   | ations of Subsampled AD-CDR                        | 85 |

|   |      | 3.7.1    | Model                                              | 85 |

|   |      | 3.7.2    | Phase Noise Simulations                            | 89 |

|   |      | 3.7.3    | Robustness Against CID                             | 89 |

|   | 3.8  | Discus   | ssion                                              | 92 |

| 4   | AD-  | CDR Architecture and Design                              | 97 |

|-----|------|----------------------------------------------------------|----|

|     | 4.1  | System Architecture                                      | 97 |

|     | 4.2  | Bang-Bang Phase Detector                                 | 98 |

|     |      | 4.2.1 Comparison of Alexander and Inverse Alexander PD   | 99 |

|     |      | 4.2.2 PD Characteristics                                 | 01 |

|     |      | 4.2.3 Performance                                        | 04 |

|     | 4.3  | Digitally Controlled Oscillator                          | 06 |

|     | 4.4  |                                                          | 08 |

|     | 4.5  |                                                          | 09 |

|     | 4.6  |                                                          | 10 |

| 5   | Circ | cuit Implementation 1                                    | 13 |

|     | 5.1  | -                                                        | 13 |

|     | 5.2  |                                                          | 15 |

|     |      | 1 6                                                      | 15 |

|     |      |                                                          | 15 |

|     |      |                                                          | 20 |

|     |      | 1 0                                                      | 20 |

|     | 5.3  |                                                          | 20 |

|     | 5.4  |                                                          | 23 |

|     | 5.5  |                                                          | 24 |

|     | 5.6  |                                                          | 24 |

|     |      |                                                          |    |

| III | [ Re | esults and Conclusions 12                                | 29 |

| 6   | Exp  |                                                          | 31 |

|     | 6.1  | 1                                                        | 31 |

|     |      | 6.1.1 Electrical Test Setup                              | 33 |

|     |      | 6.1.2 Optical Test Setup                                 | 34 |

|     | 6.2  | Electrical Tests in Continuous Mode                      | 36 |

|     |      |                                                          | 36 |

|     |      | 6.2.2 Digitally Controlled Oscillator Operation 1        | 36 |

|     |      | 6.2.3 Phase Detector Operation                           | 39 |

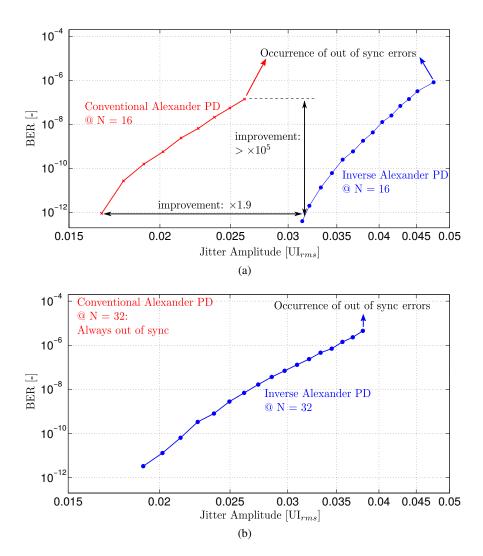

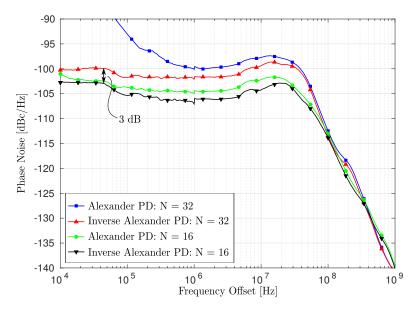

|     |      | 6.2.4 Comparison Conventional and Inverse Alexander PD 1 | 40 |

|     |      | 6.2.5 All-Digital Clock and Data Recovery Operation 1    | 42 |

|     |      | 6.2.6 Describing Function Stability Verification 1       | 48 |

|     | 6.3  | Electrical Setup Tests in Burst Mode                     | 50 |

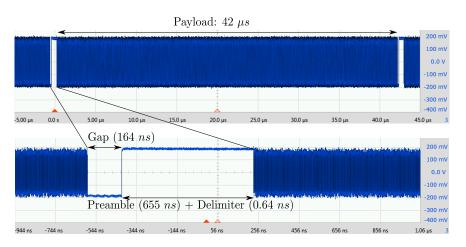

|     |      | 6.3.1 Frame Structure                                    | 50 |

|     |      | 6.3.2 Settling Time                                      | 53 |

xiii

|    | 6.4 | Optical Setup Tests in Continuous Mode | 154<br>154<br>154<br>157 |

|----|-----|----------------------------------------|--------------------------|

|    | 6.5 |                                        | 157                      |

| 7  | Con | clusion and Future Work                | 163                      |

|    | 7.1 | Conclusion                             | 163                      |

|    | 7.2 | Future Work                            | 165                      |

|    |     | 7.2.1 Possible Improvements            | 165                      |

|    |     | 7.2.2 Additional Functionalities       | 166                      |

|    |     | 7.2.3 Higher Data Rates                | 166                      |

| IV | A   | opendix                                | 171                      |

| A  | LTV | Analysis Calculations                  | 173                      |

# List of Figures

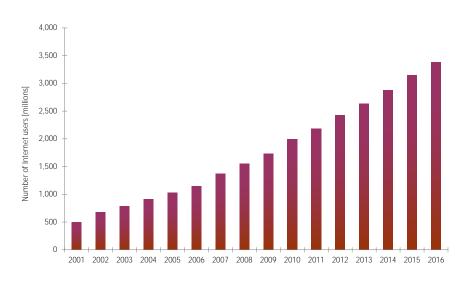

| 1.1  | The number of internet users from 2001 until 2017 [3]                   | 4  |

|------|-------------------------------------------------------------------------|----|

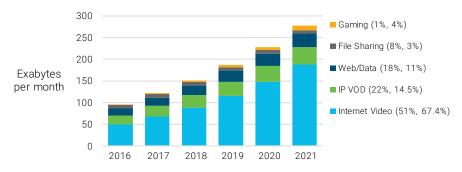

| 1.2  | The future global internet traffic by application [2]                   | 4  |

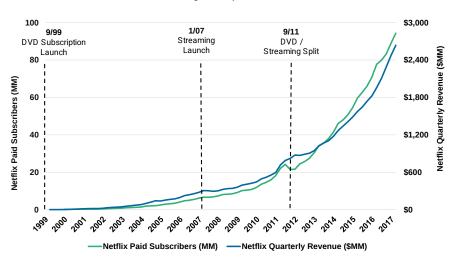

| 1.3  | The evolution of the Netflix subscribers [4]                            | 6  |

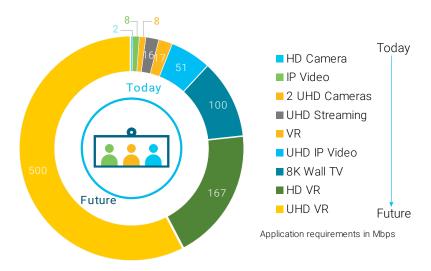

| 1.4  | The current and future video requirements [2]                           | 6  |

| 1.5  | The evolution of Facebook platform Medium Attachment                    | _  |

|      | Units (MAUs) [4]                                                        | 7  |

| 1.6  | The Compound Annual Growth Rate (CAGR) of the elec-                     |    |

|      | tricity consumption in ICT compared to the total worldwide              |    |

|      | electricity consumption. Networks is the fastest growing category [12]. | 8  |

| 1.7  | The modern telecommunication network hierarchy [14].                    | 9  |

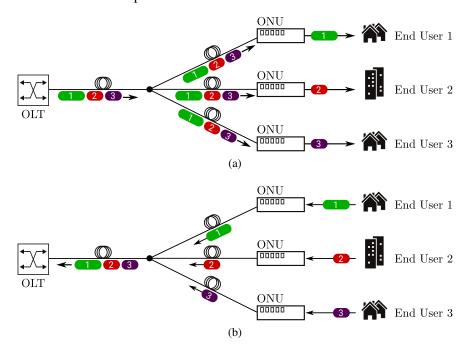

| 1.8  | A Passive Optical Network [14].                                         | 12 |

| 1.9  | The communication in PON: (a) downstream and (b) up-                    |    |

| 117  | stream.                                                                 | 13 |

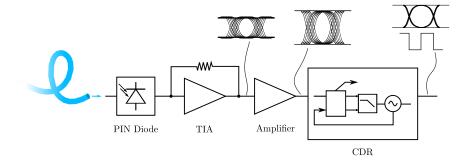

| 1.10 |                                                                         | 14 |

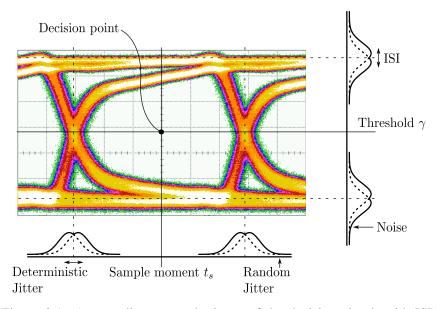

| 2.1  | An eye diagram at the input of the decision circuit with ISI,           |    |

|      | noise and jitter.                                                       | 22 |

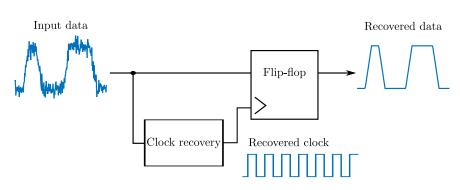

| 2.2  | A basic block diagram of a Clock and Data Recovery circuit.             | 24 |

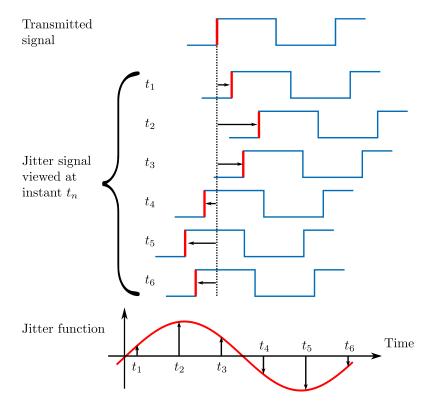

| 2.3  | Jitter: unwanted phase variations of a signal                           | 25 |

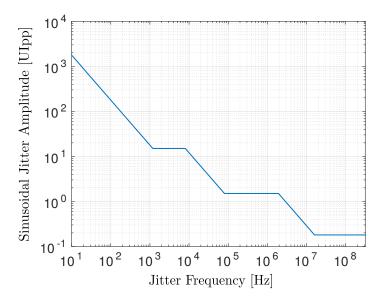

| 2.4  | The jitter tolerance mask for SDH STM-256 [9]                           | 27 |

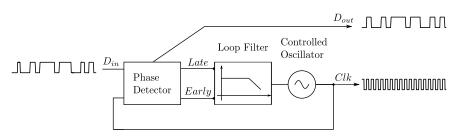

| 2.5  | A block diagram of a PLL-based CDR circuit                              | 31 |

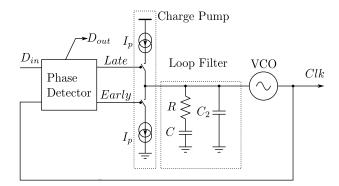

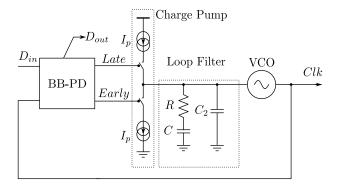

| 2.6  | A charge pump PLL-based CDR circuit.                                    | 31 |

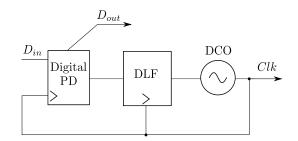

| 2.7  | An All-Digital CDR.                                                     | 33 |

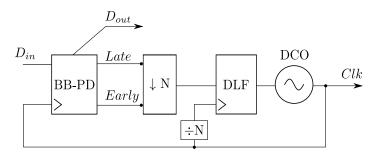

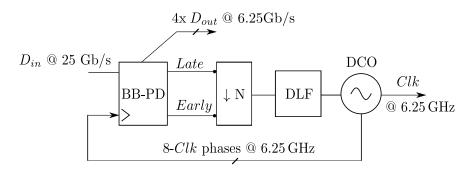

| 2.8  | The proposed next-generation All-Digital CDR                            | 37 |

| 3.1  | A charge pump Phase Locked Loop-based Clock and Data                    |    |

|      | Recovery circuit.                                                       | 49 |

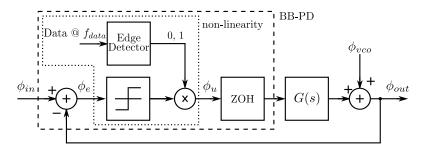

| 3.2  | The behavioral model of a CDR with a BB-PD.                             | 49 |

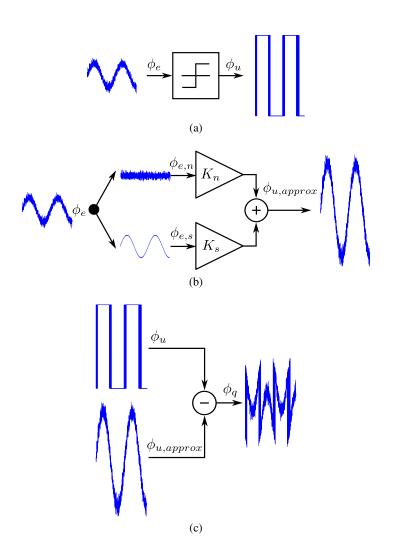

| 3.3  | A time domain example of the describing function model<br>for a non-linearity. (a) The characteristic of a comparator<br>(a non-linearity). (b) The describing function characteristic<br>according to the original approach in [8]. (c) The definition<br>of the linearization error $\phi_q$ , which is included in [2] and in<br>our pseudo-linear analysis | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

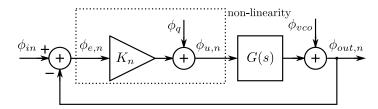

| 3.4  | The RIDF model of a CDR with a BB-PD                                                                                                                                                                                                                                                                                                                           | 53 |

| 3.5  | The GSIDF model of the non-linearity of a BB-PD                                                                                                                                                                                                                                                                                                                | 54 |

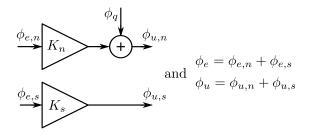

| 3.6  | $K_s$ according to Eq. (3.15) as a function of the amplitude $A_e$ and the RMS jitter $\sigma_e$ at the input of the non-linearity.<br>( $\alpha = 0.5$ )                                                                                                                                                                                                      | 56 |

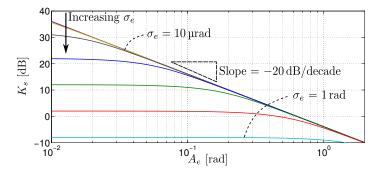

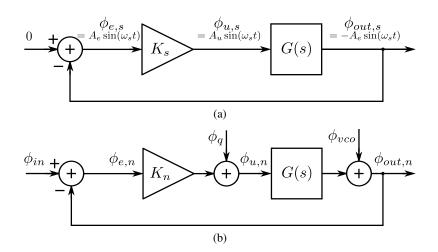

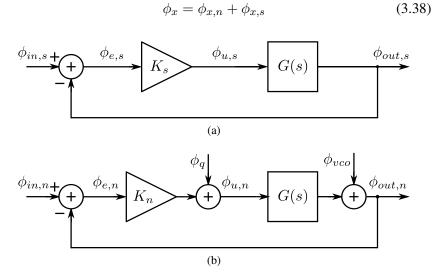

| 3.7  | The GSIDF model of a CDR with a BB-PD for (a) the sinusoidal component and (b) the random Gaussian component (identical to the RIDF model in Fig. 3.4).                                                                                                                                                                                                        | 57 |

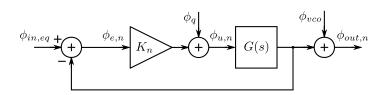

| 3.8  | The altered GSIDF model of a CDR with a BB-PD for<br>the random Gaussian component (equivalent to the RIDF<br>model in Fig. 3.4)                                                                                                                                                                                                                               | 59 |

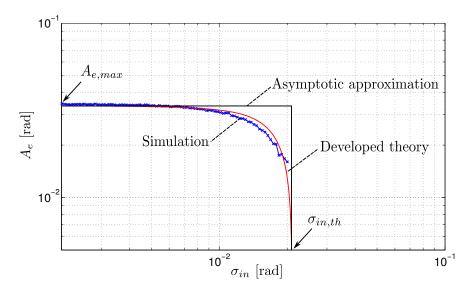

| 3.9  | The limit cycle amplitude $A_e$ as a function of the RMS in-<br>put jitter $\sigma_{in}$ . The simulation results where performed with:<br>$f_{data} = 10 \text{ GHz}, \ \omega_z = 2\pi \cdot 300 \text{ kHz}, \ \omega_0 = 2\pi \cdot 3 \text{ MHz}, \ \omega_p = 2\pi \cdot 30 \text{ MHz}$ and $T_d = 3 \text{ ns.} \dots \dots \dots \dots \dots \dots$   | 61 |

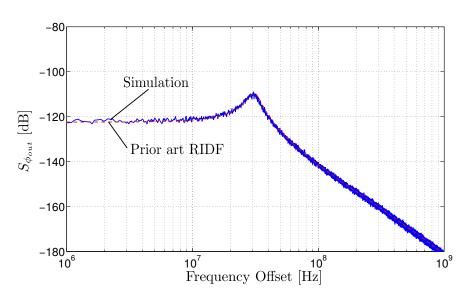

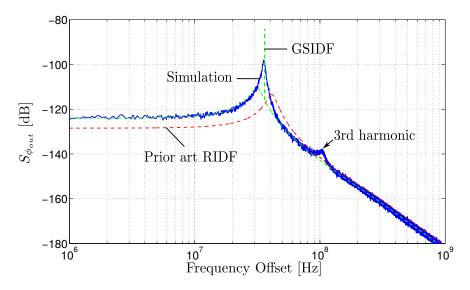

| 3.10 | The power spectrum $S_{\phi_{out}}$ of the same CDR as in Fig. 3.9 for an input noise level $\sigma_{in} = \sqrt{2} \cdot \sigma_{in,th}$ .                                                                                                                                                                                                                    | 62 |

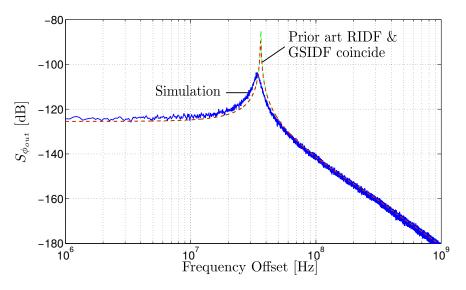

| 3.11 | The power spectrum $S_{\phi_{out}}$ of the same Clock and Data Re-<br>covery (CDR) as in Fig. 3.9 for an input noise level $\sigma_{in} = \frac{\sigma_{in,th}}{\sqrt{2}}$ . The simulation results are compared to the pre-<br>diction where the CDR does not contain any limit cycles:<br>i.e. the RIDF and to the prediction where a limit cycle is         |    |

|      | present in the CDR: i.e. the GSIDF                                                                                                                                                                                                                                                                                                                             | 62 |

| 3.12 | The power spectrum $S_{\phi_{out}}$ of the same CDR as in Fig. 3.9 for an input noise level $\sigma_{in} = \sigma_{in,th}$ .                                                                                                                                                                                                                                   | 63 |

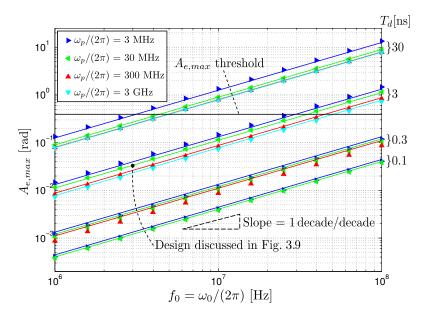

| 3.13 | The worst-case limit cycle amplitude $A_{e,max}$ as a function<br>of the gain $\omega_0$ for different pole frequencies $\omega_p$ and delays<br>$T_d$ . The corresponding calculated results (solid lines) and<br>simulation results (markers) are represented with the same                                                                                  |    |

|      | color                                                                                                                                                                                                                                                                                                                                                          | 66 |

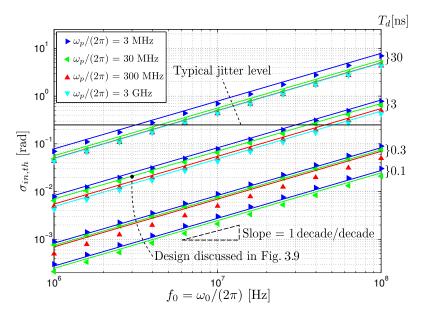

| 3.14 | The threshold RMS input jitter $\sigma_{in,th}$ as a function of the gain $\omega_0$ for different pole frequencies $\omega_p$ and delays $T_d$ .<br>The corresponding calculated results (solid lines) and simulation results (markers) are represented with the same color. | 67       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

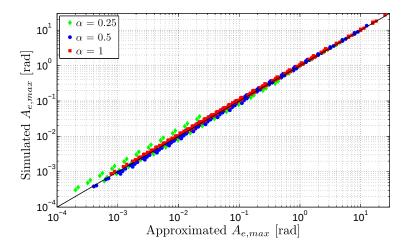

| 3.15 | A scatter plot of simulated $A_{e,max}$ as a function of the approximation according to Eq. (3.27) for different values of $\omega_0, \omega_p, T_d$ and $\alpha$ .                                                                                                           | 70       |

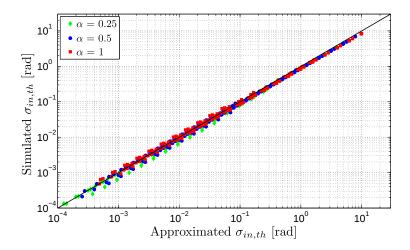

| 3.16 | A scatter plot of simulated $\sigma_{in,th}$ as a function of the approximation according to Eq. (3.31) for different values of $\omega_0, \omega_p, T_d$ and $\alpha$ .                                                                                                      | 70       |

| 3.17 | The GSIDF model of a CDR with a BB-PD for the jitter tolerance measurements with the block diagram for (a) the sinusoidal component and (b) the random Gaussian com-                                                                                                          |          |

|      | ponent (identical to the RIDF model in Fig. 3.4).                                                                                                                                                                                                                             | 74       |

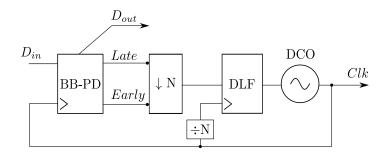

| 3.18 | A block diagram of the proposed next-generation All-Digital                                                                                                                                                                                                                   |          |

|      | CDR                                                                                                                                                                                                                                                                           | 76       |

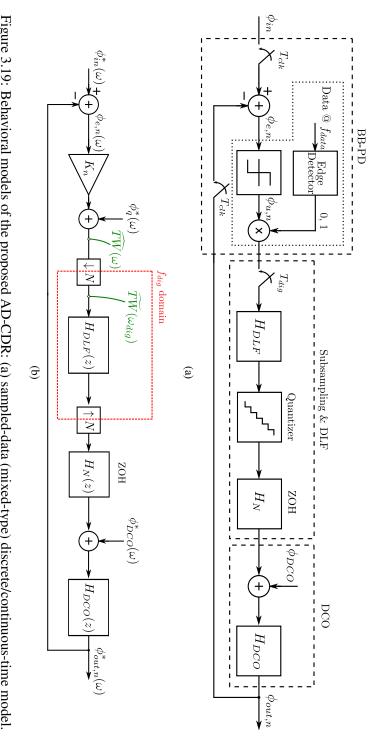

| 3.19 | Behavioral models of the proposed AD-CDR: (a) sampled-<br>data (mixed-type) discrete/continuous-time model. (b) discrete<br>time multirate model.                                                                                                                             | e-<br>78 |

| 2 20 | The phase noise through the AD-CDR: a transformed phase                                                                                                                                                                                                                       | 70       |

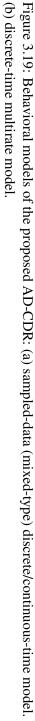

| 3.20 | domain model of the input branch                                                                                                                                                                                                                                              | 79       |

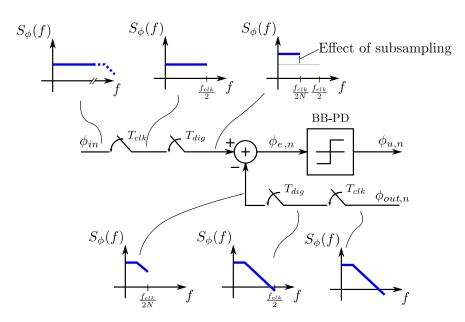

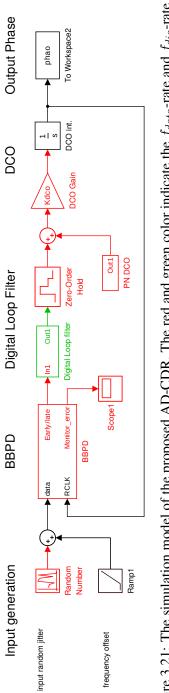

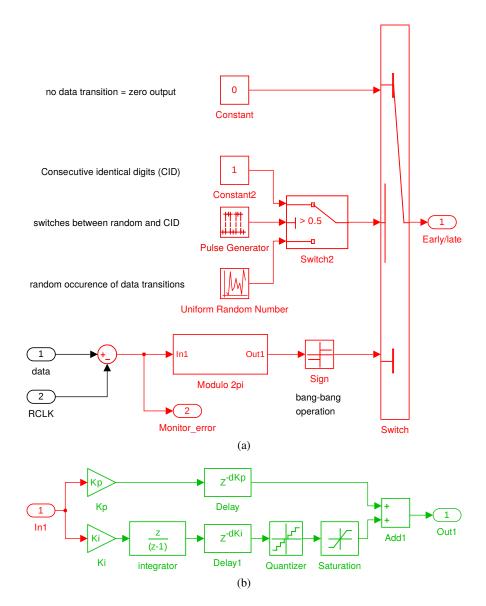

| 3.21 | The simulation model of the proposed AD-CDR. The red and green color indicate the $f_{data}$ -rate and $f_{dig}$ -rate operation, respectively.                                                                                                                               | 87       |

| 3.22 | Details of the simulation model of the proposed AD-CDR<br>in Fig. 3.21 with (a) the BB-PD building block and (b) the<br>DLF building block. The red and green color indicate the                                                                                              |          |

|      | $f_{data}$ -rate and $f_{dig}$ -rate operation, respectively.                                                                                                                                                                                                                 | 88       |

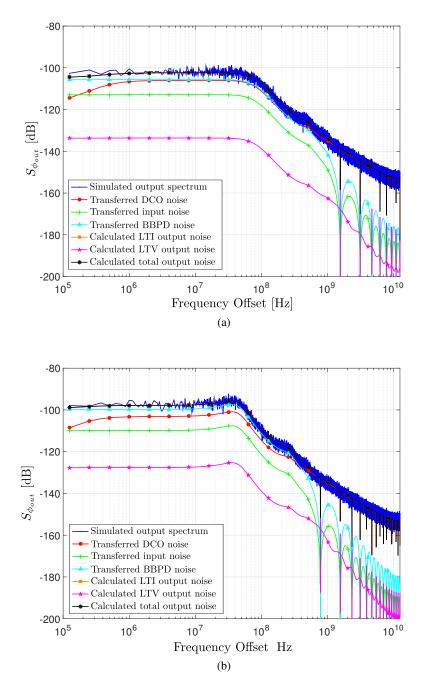

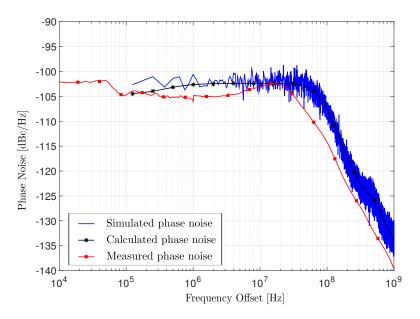

| 3.23 | Phase noise simulations with the different noise contribu-<br>tions derived from the LTV analysis with subsample fac-                                                                                                                                                         |          |

|      | tors: (a) $N = 16$ and (b) $N = 32$                                                                                                                                                                                                                                           | 90       |

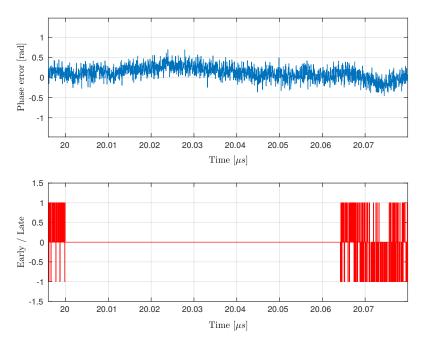

| 3.24 | An example of the simulation results for the case where the subsampled PD output consists of $l = 100$ idle values (= 64                                                                                                                                                      |          |

|      | ns idle time )                                                                                                                                                                                                                                                                | 91       |

| 4.1  | The system diagram of the AD-CDR                                                                                                                                                                                                                                              | 98       |

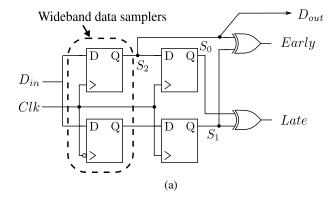

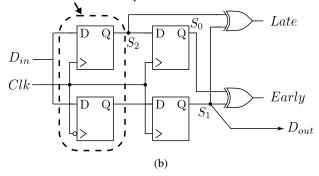

| 4.2  | (a) The conventional Alexander PD and (b) the Inverse Alexan-                                                                                                                                                                                                                 | -        |

|      | der PD circuit.                                                                                                                                                                                                                                                               | 100      |

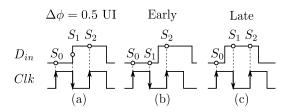

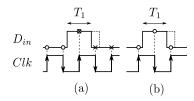

| 4.3  | Waveforms for the locking behavior of the Alexander PD :<br>(a) Ideal locking condition with phase difference $\Delta \phi = 0.5$<br>UI; (b) <i>Early</i> condition; (c) <i>Late</i> condition                                                                                                                                                              | 100      |

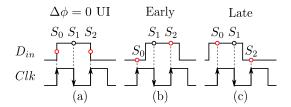

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.4  | Waveforms for the locking behavior of the Inverse Alexan-<br>der PD : (a) Ideal locking condition with phase difference<br>$\Delta \phi = 0$ UI; (b) <i>Early</i> condition; (c) <i>Late</i> condition                                                                                                                                                      | 101      |

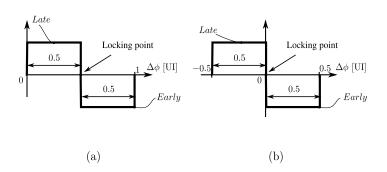

| 4.5  | Simplified (single pulse) PD output characteristics at full rate operation for the case of ideal waveforms: (a) the Alexander PD , (b) the Inverse Alexander                                                                                                                                                                                                | 102      |

| 4.6  | Simplified (single pulse) PD output characteristics at full rate operation for the case of duty-cycle distortion: (a) the Alexander PD and (b) the Inverse Alexander PD                                                                                                                                                                                     | 102      |

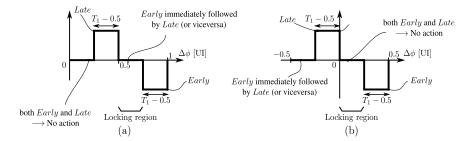

| 4.7  | PD waveforms for data with duty-cycle distortion corresponding to the anomalous cases (a) Alexander <i>Early</i> immediately followed by <i>Late</i> (most relevant for conventional Alexander), and (b) Simultaneous <i>Early</i> and <i>Late</i> (most relevant for Inverse Alexander).                                                                   | 103      |

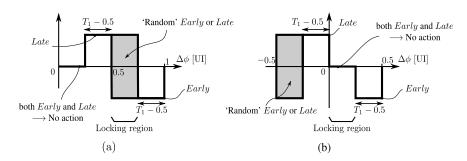

| 4.8  | Simplified (single pulse) PD output characteristics at sub-<br>sampled rate operation: (a) the Alexander PD for the case<br>of duty-cycle distortion and (b) the Inverse Alexander PD<br>for the case of duty-cycle distortion.                                                                                                                             | 104      |

| 4.9  | Simulink simulations of the locking behavior in the case<br>of a pronounced duty-cycle distortion with (a) the eye dia-<br>gram of input data, (b) the persistence view of the recovered<br>clock of a CDR with a conventional Phase Detector, and (c)<br>the persistence view of the recovered clock of a CDR with<br>an Inverse Alexander Phase Detector. | 105      |

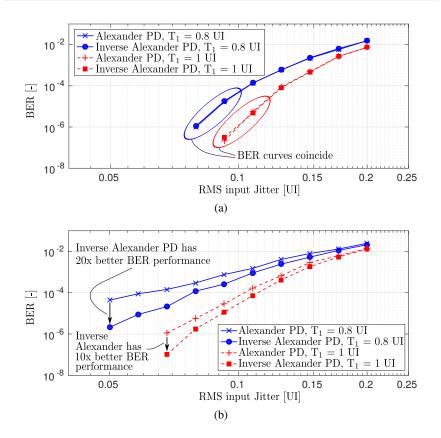

| 4.10 | The BER performance: (a) no subsampling; (b) subsample factor = 4                                                                                                                                                                                                                                                                                           | 107      |

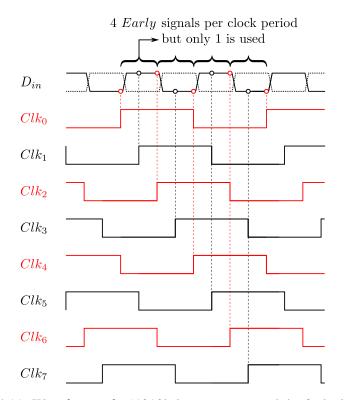

| 4.11 | Waveforms of a '1010' data sequence and the 8 clock phases when the AD-CDR is <i>Early</i> . The red clock phases correspond to edge-related samples and the black to data-related samples (as in Fig. 4.4).                                                                                                                                                | 108      |

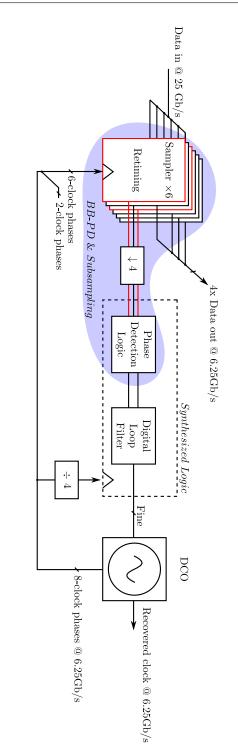

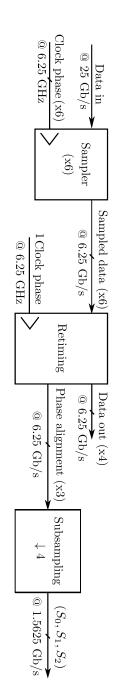

| 5.1  | The block diagram of AD-CDR implementation (speeds are in dicated for $25 \text{ Gb/s}$ operation). Red is used for edge-related samples and black for data-related samples (as in Fig. 4.4).                                                                                                                                                               | -<br>114 |

|      |                                                                                                                                                                                                                                                                                                                                                             |          |

xviii

| 5.2  | A detail of the full custom part of the <i>BB-PD</i> & <i>Subsampling</i> , which contains 6 samplers, a retiming block and a   |       |

|------|---------------------------------------------------------------------------------------------------------------------------------|-------|

|      | subsampling block (speeds are indicated for $25 \mathrm{Gb/s}$ operation)                                                       | 116   |

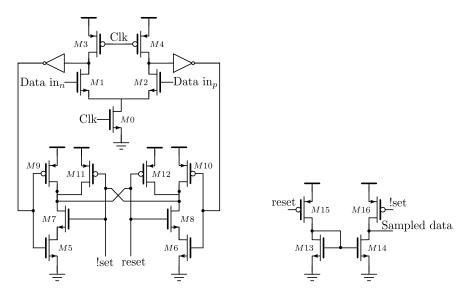

| 5.3  | ation)                                                                                                                          | 110   |

| 5.5  | sense amplifier input and a slower regenerative latch.                                                                          | 117   |

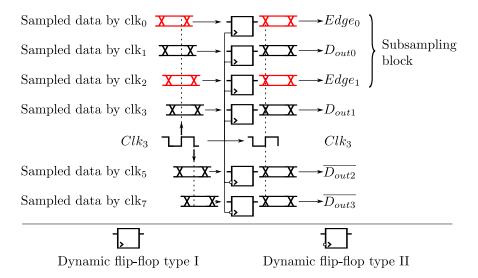

| 5.4  | The retiming circuit consisting of an array of retiming type                                                                    |       |

|      | I (postive edge triggered) flip-flops and an array of type II                                                                   |       |

|      | (negative edge triggered) flip-flops. Red is used for edge-                                                                     |       |

|      | related samples and black for data-related samples (as in Fig. 4.4).                                                            | 118   |

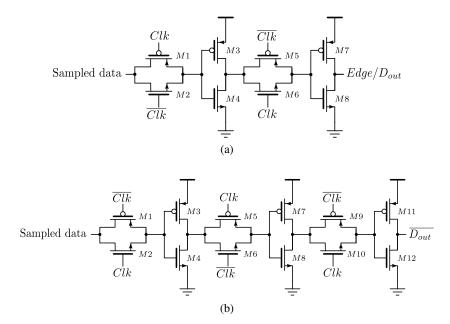

| 5.5  | The flip-flops used in the retiming circuit: (a) type I (posi-                                                                  | 110   |

| 5.5  | tive edge triggered) dynamic flip-flop and (b) type I (post-                                                                    |       |

|      | ative edge triggered) dynamic flip-flop                                                                                         | 119   |

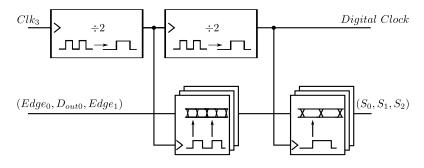

| 5.6  | The subsampling circuit.                                                                                                        | 120   |

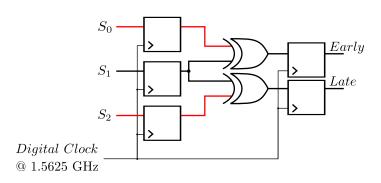

| 5.7  | The digital phase detection logic                                                                                               | 121   |

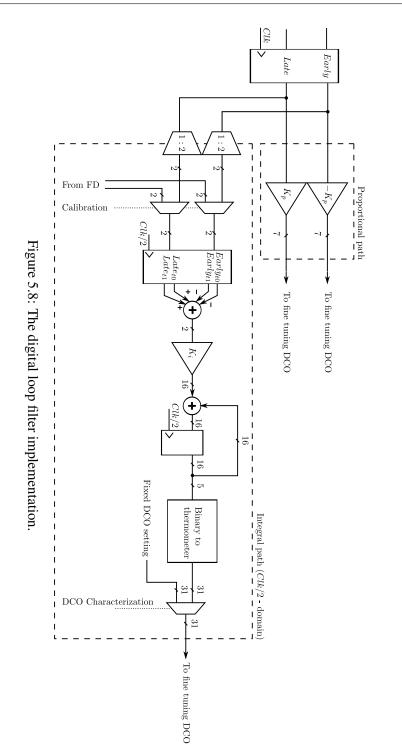

| 5.8  | The digital loop filter implementation.                                                                                         | 122   |

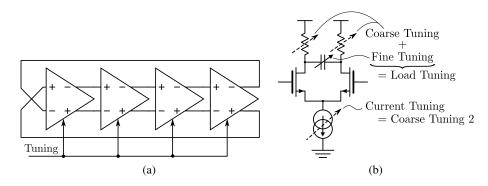

| 5.9  | The DCO structure: (a) ring oscillator and (b) delay cell                                                                       | 123   |

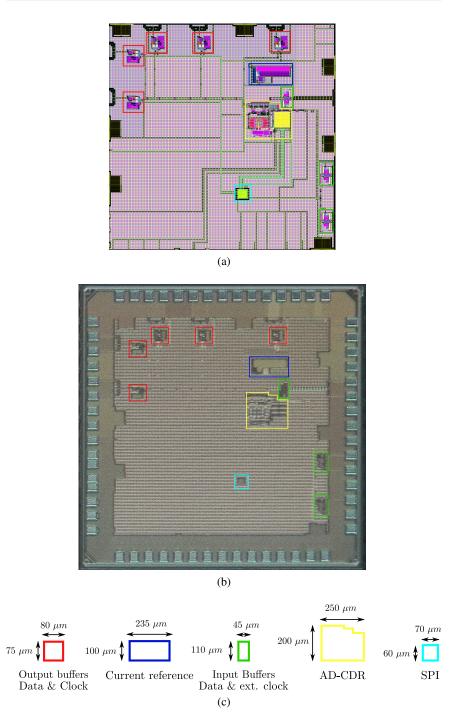

| 5.10 | The complete AD-CDR ASIC: (a) the drawn layout, (b) a                                                                           |       |

|      | photo of manufactured ASIC and (c) the legend                                                                                   | 125   |

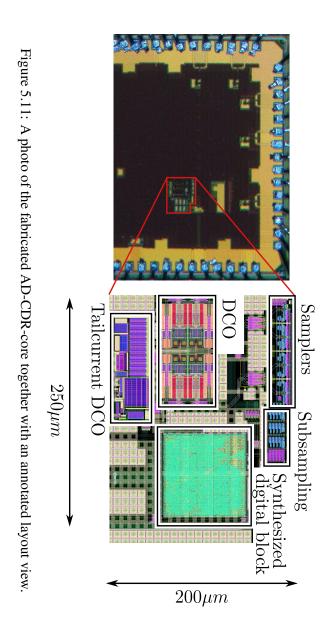

| 5.11 | A photo of the fabricated AD-CDR-core together with an                                                                          | 100   |

|      | annotated layout view.                                                                                                          | 126   |

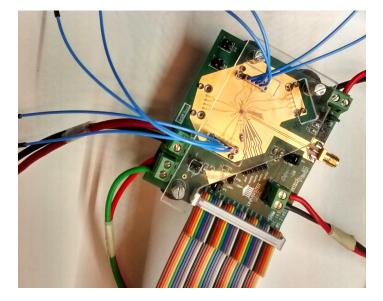

| 6.1  | The AD-CDR testboard.                                                                                                           | 132   |

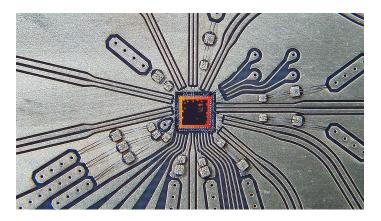

| 6.2  | A photo of the implemented chip wire bonded on a high-                                                                          |       |

|      | speed PCB                                                                                                                       | 132   |

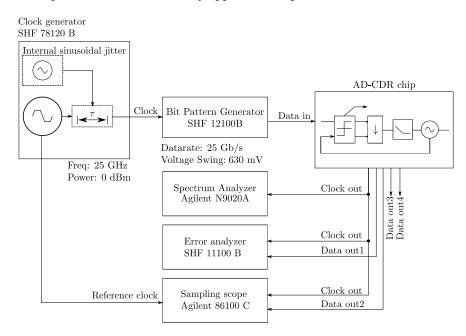

| 6.3  | The electrical test setup with AD-CDR                                                                                           | 133   |

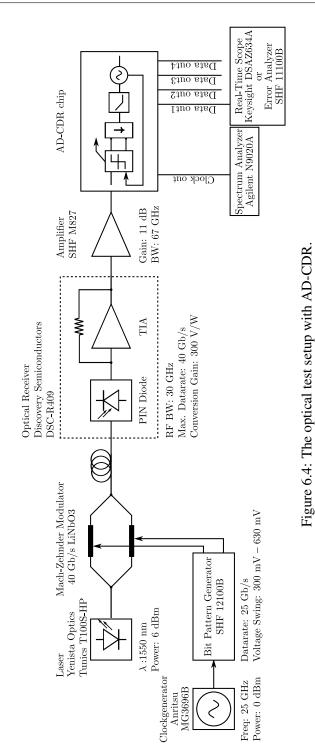

| 6.4  | The optical test setup with AD-CDR.                                                                                             | 135   |

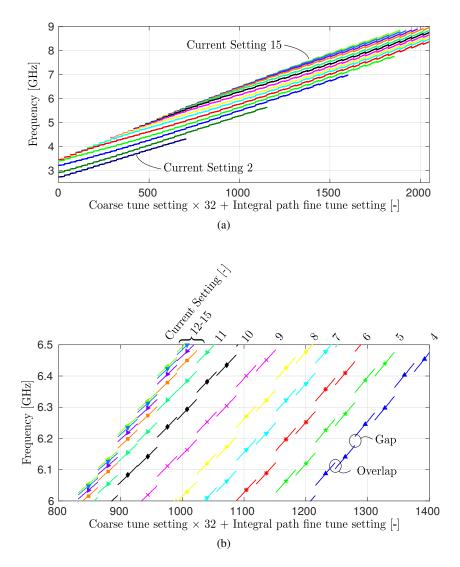

| 6.5  | The free running frequency of the DCO with (a) an overview the complete frequency range and (b) a detail around 6.25 CII        | - 127 |

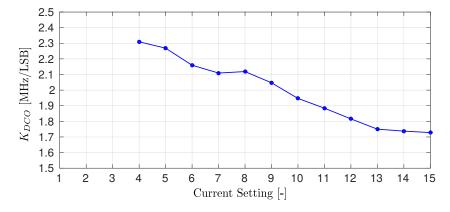

| 6.6  | the complete frequency range and (b) a detail around $6.25 \text{ GH}$<br>The gain of the DCO $K_{dco}$ at $6.25 \text{ GHz}$ . | 138   |

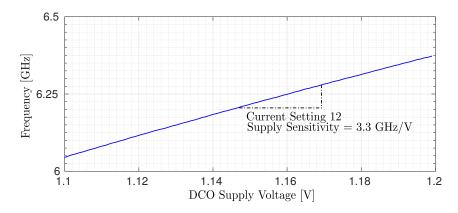

| 6.7  | The supply sensitivity at $6.25 \text{ GHz}$ .                                                                                  |       |

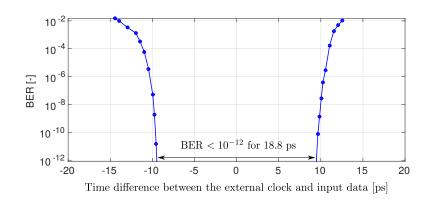

| 6.8  | The sensitivity of the PD with a PRBS7 input data at $25 \text{ Gb/s}$                                                          |       |

| 6.9  | The measured BER for the conventional and the Inverse                                                                           | .140  |

| 0.7  | Alexander phase detector with a PRBS7 input data sequence                                                                       |       |

|      | at 25 Gb/s: (a) with a subsample factor $N = 16$ and (b)                                                                        |       |

|      | with a subsample factor $N = 32$ . (Digital Loop Filter set-                                                                    |       |

|      | tings: $K_p = 5$ and $K_i = 2^{-7}$ )                                                                                           | 141   |

| 6.10 | The phase noise of the recovered clock with a PRBS31 in-<br>put data sequence at 25 Gb/s: Comparison between Alexan-<br>der and Inverse Alexander PD for different subsample fac-<br>tors (i.e. $N = 16$ and $N = 32$ ). (Digital Loop Filter<br>settings: $K_p = 5$ and $K_i = 2^{-7}$ ) | 142 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

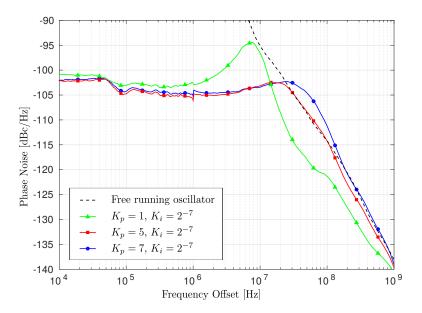

| 6.11 | The phase noise of the recovered clock with a PRBS31 in-<br>put data sequence at 25 Gb/s: Sweep $K_p$                                                                                                                                                                                     | 143 |

| 6.12 |                                                                                                                                                                                                                                                                                           | 144 |

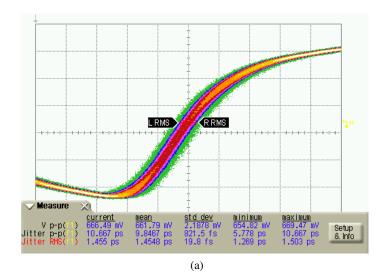

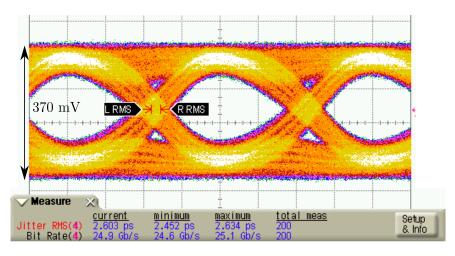

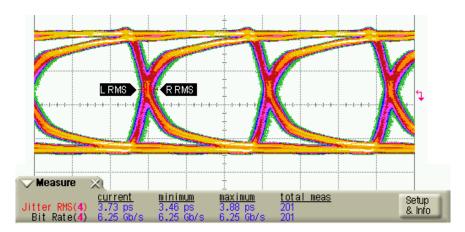

| 6.13 | Persistence plots of (a) the recovered (differential) clock<br>(jitter < 1.5 ps <sub>rms</sub> ) and (b) the recovered data (jitter $\approx 3.71$ ps <sub>rn</sub>                                                                                                                       |     |

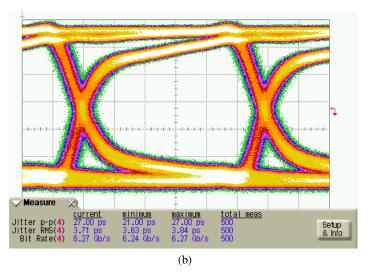

| 6 14 | The jitter tolerance with a PRBS7 input data sequence at                                                                                                                                                                                                                                  | 145 |

|      | $25 \text{ Gb/s:}$ (a) Sweep $K_p$ and (b) Sweep $K_i$ .                                                                                                                                                                                                                                  | 146 |

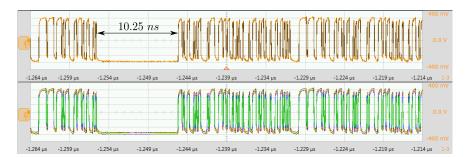

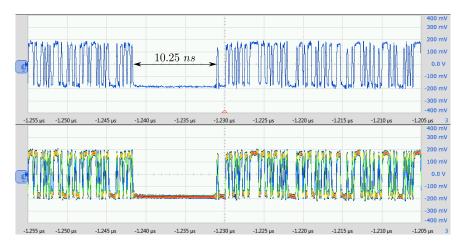

| 6.15 | A packet in electrical burst mode measurements with a short gap (10.25 ns).                                                                                                                                                                                                               | 151 |

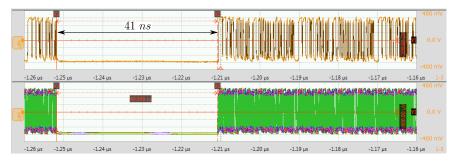

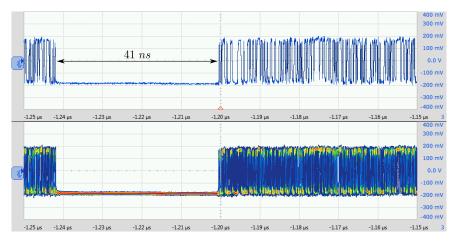

| 6.16 | A packet in electrical burst mode measurements with a long gap (41 ns).                                                                                                                                                                                                                   | 151 |

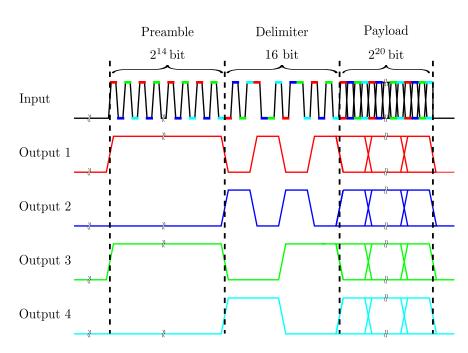

| 6.17 |                                                                                                                                                                                                                                                                                           | 152 |

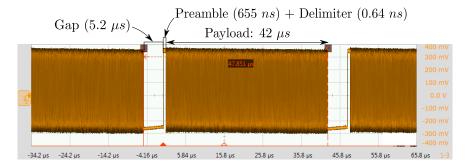

| 6.18 | A captured 6.25 Gb/s output stream in electrical burst mode measurements.                                                                                                                                                                                                                 | 152 |

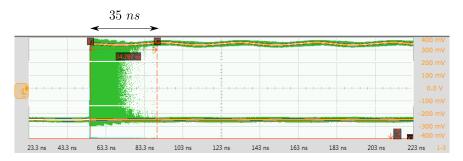

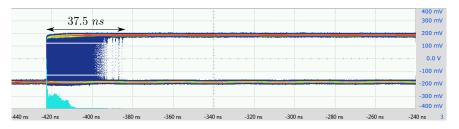

| 6.19 | The AD-CDR is always in lock after 35 ns for 2 million packets with setting $K_p = 7$ and $K_i = 2^{-9}$ .                                                                                                                                                                                | 153 |

| 6.20 | The eye diagram of the input signal of the CDR (PRBS9 @ $25 \text{ Gb/s}$ ).                                                                                                                                                                                                              | 154 |

| 6.21 | The eye diagram of one of the quarter-rate outputs of the CDR (@ $6.25 \text{ Gb/s}$ ).                                                                                                                                                                                                   | 155 |

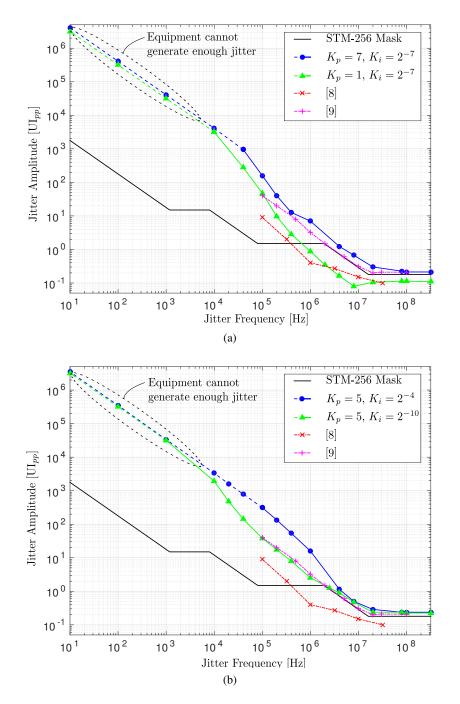

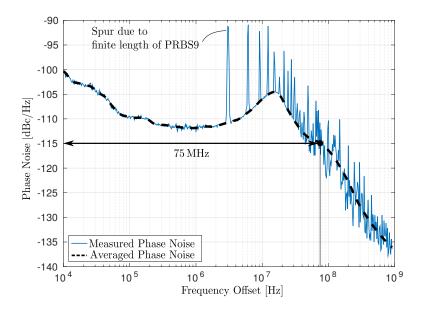

| 6.22 | The phase noise of the quarter-rate recovered clock of the AD-CDR for a PRBS9 input data sequence at 25 Gb/s ( $K_p =$                                                                                                                                                                    | 155 |

| ( )) | 5, $K_i = 2^{-7}$ )                                                                                                                                                                                                                                                                       | 156 |

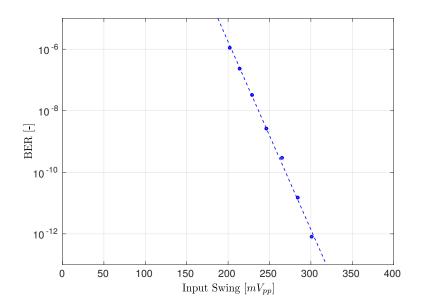

| 0.23 | The BER as a function of the voltage swing at the input of the AD-CDR.                                                                                                                                                                                                                    | 156 |

| 6.24 | A packet in optical burst mode measurements with a short gap $(10.25 \text{ ns})$ .                                                                                                                                                                                                       | 158 |

| 6.25 | A packet in optical burst mode measurements with a long                                                                                                                                                                                                                                   |     |

|      | gap (41 ns)                                                                                                                                                                                                                                                                               | 158 |

| $6.26$ A captured $6.25\mathrm{Gb/s}$ output stream in optical burst mode | 2     |

|---------------------------------------------------------------------------|-------|

| measurements                                                              | . 159 |

| 6.27 The AD-CDR is always in lock after 37.5 ns for 2 million             | 1     |

| packets with setting $K_p = 5$ and $K_i = 2^{-7}$ .                       | . 159 |

# List of Tables

| 1.1 | An Italian network forecast (2015-2020): device density<br>and energy requirements in the Business-As-Usual (BAU)<br>case [15] | 10  |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | The advantages of optical fiber [16]                                                                                           | 11  |

| 3.1 | The model parameters of the complete linearized discrete-<br>time multirate AD-CDR model shown in Fig. 3.19(b)                 | 81  |

| 5.1 | The device sizes of the sense amplifier flip-flop shown in                                                                     |     |

|     | Fig. 5.3                                                                                                                       | 117 |

| 5.2 | The device sizes of the dynamic flip-flops shown in Fig. 5.5.                                                                  | 119 |

| 6.1 | The comparison of digital CDRs                                                                                                 | 147 |

# Glossary

### A

| AD-CDR | All-Digital Clock and Data Recovery     |

|--------|-----------------------------------------|

| AD-PLL | All-Digital Phase Locked Loop           |

| ASIC   | Application Specific Integrated Circuit |

### B

| BAU   | Business-As-Usual        |

|-------|--------------------------|

| BB-PD | Bang-Bang Phase Detector |

| BER   | Bit-Error Rate           |

| BiPON | Bit-interleaving PON     |

| BM-Rx | Burst Mode Receiver      |

# С

| CAGR | Compound Annual Growth Rate  |

|------|------------------------------|

| CBI  | Cascaded BiPON               |

| CDR  | Clock and Data Recovery      |

| CID  | Consecutive Identical Digits |

## D

| DCO | Digitally Controlled Oscillator |

|-----|---------------------------------|

| DLF | Digital Loop Filter             |

| DLL | Delay Locked Loop               |

| DPRBS | Differentiated Pseudo Random Bit Sequence |

|-------|-------------------------------------------|

| DUT   | Device Under Test                         |

|       |                                           |

#### F

| FTTC | Fibre-To-The-Curb     |

|------|-----------------------|

| FTTH | Fibre-To-The-Home     |

| FTTP | Fiber-To-The-Premises |

#### G

| GSIDF | Gaussian-plus-Sinusoid-Input Describing Func- |

|-------|-----------------------------------------------|

|       | tion                                          |

| GVCO  | Gated Voltage Controlled Oscillator           |

## I

| ICT   | Information and                          | l Communications Techno | ology  |

|-------|------------------------------------------|-------------------------|--------|

| IL    | Injection Locke                          | d                       |        |

| ISI   | InterSymbol Int                          | terference              |        |

| ITU-T | International                            | Telecommunications      | Union, |

|       | Telecommunication Standardization Sector |                         |        |

### L

| LSB | Least Significant Bit |

|-----|-----------------------|

| LTI | Linear Time-Invariant |

| LTV | Linear Time-Variant   |

#### Μ

| MAUs | Medium Attachment Units |

|------|-------------------------|

| MZM  | Mach-Zehnder Modulator  |

#### xxvi

### Ν

| NG-EPON | Next-Generation Ethernet PON |

|---------|------------------------------|

| NRZ     | Non-Return-to-Zero           |

## 0

| OLT | Optical Line Terminal |

|-----|-----------------------|

| ONU | Optical Network Unit  |

#### Р

| PAM-4 | 4-level Pulse- Amplitude Modulation |

|-------|-------------------------------------|

| PCB   | Printed Circuit Board               |

| PD    | Phase Detector                      |

| PI    | Phase Interpolator                  |

| PLL   | Phase Locked Loop                   |

| PON   | Passive Optical Network             |

| PRBS  | Pseudo Random Bit Sequence          |

|       |                                     |

## R

| tion |

|------|

| 2    |

#### S

| SDH  | Synchronous Digital Hierarchy        |

|------|--------------------------------------|

| SIDF | Sinusoidal-Input Describing Function |

| SNR  | Signal-to-Noise Ratio                |

| STM  | Synchronous Transport Module         |

#### Т

| •    | ٠ | ٠ |

|------|---|---|

| XXV1 | 1 | 1 |

| TDC<br>TIA | Time-to-Digital Converter<br>TransImpedance Amplifier |

|------------|-------------------------------------------------------|

| U          |                                                       |

| UHD<br>UI  | Ultra-High-Definition<br>Unit Interval                |

| V          |                                                       |

| VCO        | Voltage Controlled Oscillator                         |

| Z          |                                                       |

| ZOH        | Zero-Order Hold                                       |

# Nederlandstalige Samenvatting –Dutch Summary–

De laatste jaren is het dataverkeer exponentieel gestegen en er wordt voorspeld dat het einde van deze groei nog steeds niet in zicht is. Door een stijgend aanbod aan nieuwe online toepassingen, binnen sectoren zoals amusement, handel, industrie en gezondheidszorg vraagt men steeds meer bandbreedte en stelt men steeds hogere eisen aan de kwaliteit van de netwerk- en ICT-infrastructuur. Vooral de explosieve groei van online video en clouddiensten vereist hogere datasnelheden.

In de huidige internetarchitectuur zijn eindgebruikers verbonden met het openbare netwerk via het toegangsnetwerk van de lokale internetaanbieder. Tegenwoordig worden er nieuwe passieve optische netwerken (PONs) toegepast. Door gebruik te maken van optische vezels kan men veel hogere datasnelheden aanbieden en dit voor een fractie van het vermogenverbruik. Desondanks heeft onderzoek aangetoond dat het vermogenverbruik van communicatienetwerken een significant en groeiend deel van het totale globale vermogenverbruik inneemt. Meer en meer wordt men er zich nu van bewust dat dit een negatieve impact op het milieu heeft.

Dit heeft geleid tot de oprichting van het GreenTouch consortium in 2010. Deze instantie concentreert zich vooral op de vraag naar de stijgende datasnelheden, maar besteedt tevens ook aandacht aan de ecologische en economische impact ervan. De missie bestaat erin om aan te tonen dat de energieefficiëntie van communicatienetwerken kan worden geoptimaliseerd met een factor  $1000 \times$  tegen 2020, in vergelijking met het door GreenTouch gedefinieerd referentienetwerk dat opgebouwd werd met de meest energieefficiënte apparatuur die in 2010 beschikbaar was.

Een belangrijke component van een optische ontvanger in een passief optisch toegangsnetwerk zijn klok-en-data-extractie (CDR) schakelingen. Deze CDR-schakelingen worden momenteel geïmplementeerd met omvangrijke en vermogensinefficiënte bouwblokken en hebben dus veel ruimte voor verbetering. In dit proefschrift wordt het onderzoek over onderbemonsterende technieken met laag vermogen voor een volledig gedigitaliseerde klok-endata-extractie uiteengezet. Deze technieken vormen een antwoord op de verschillende uitdagingen waarmee de volgende generatie netwerken zullen geconfronteerd worden. Om deze technieken en stelling te staven, werd een prototype van een volledig gedigitaliseerde 25 Gb/s klok-endata-extractie (AD-CDR) schakeling geïmplementeerd in een geavanceerde CMOS-technologie (40 nm).

Dankzij de digitale architectuur kon de actieve chip-oppervlakte zeer compact gehouden worden. De oppervlakte bedraagt slechts  $0.050 \text{ mm}^2$ , wat beduidend lager is dan in andere vergelijkbare onderzoeken. De vermogenefficiëntie van de kern van de CDR is 1.8 pJ/b, wat ook beter is dan de allernieuwste CDR-systemen. Bovendien is de AD-CDR uitermate aanpasbaar: de karakteristieken van het lusfilter kunnen aangepast worden om aan meerdere jitter tolerantie specificaties te voldoen. Daarnaast kan het werkingsgebied aangepast worden van 12.5 Gb/s tot 25 Gb/s. Dit is het grootste werkingsgebied van elke digitale CDR dat geen gebruik maakt van een hoogkwalitatieve, multi-gigahertz referentieklok. Vanwege het daadwerkelijke digitale karakter van de aanpasbaarheid van de frequentie, schaalt het vermogenverbruik rechtevenredig met de datasnelheid. Hierdoor wordt een uitstekende vermogenefficiëntie over het volledige werkingsgebied bereikt: het vermogenverbruik is 46 mW aan 25 Gb/s, terwijl aan 12.5 Gb/s dit slechts 23 mW is.

Bovendien is AD-CDR ook geschikt om pakketgebaseerde data te ontvangen. De pakketgebaseerde operatie van de CDR wordt mogelijk gemaakt doordat de frequentie constant blijft tussen de pakketten en doordat de lusfilterparameters aangepast kunnen worden om een grotere bandbreedte te bekomen. Deze eigenschappen zorgen ervoor dat men korte insteltijden kan bereiken. Bijgevolg heeft de AD-CDR geen hoog-accurate referentieklok nodig en is er ook geen startsignaal nodig dat aangeeft wanneer de pakketten ontvangen worden. De digitaalgestuurde oscillator (DCO) moet enkel eenmalig gekalibreerd worden, zodat de oscillatiefrequentie de datasnelheid benadert. De integratie van de CDR in een systeem wordt hierdoor enorm vereenvoudigd.

Het proefschrift bevat zeven hoofdstukken en een appendix: Hoofdstuk 1 beschrijft de impact van de stijgende vraag naar hogere datasnelheden in combinatie met een lager vermogenverbruik in de communicatienetwerken. Vervolgens wordt de huidige kern-metro-toegangsnetwerkarchitectuur voorgesteld. Typische getallen tonen aan waarom het vermogenverbruik van het toegangsnetwerk het leeuwendeel van het totale vermogenverbruik voor zich neemt. Dit is vooral te wijten aan het enorm aantal apparaten in het netwerk. In het toegangsnetwerk wordt o.a. de evolutie naar optische toegangsnetwerken en het concept van passieve optische netwerken besproken.

Hoofdstuk 2 introduceert de CDR-schakelingen en accentueert het belang van deze schakelingen. Aanvullend worden de performantiemaatstaven en een beknopt overzicht van de verschillende CDR-types weergegeven. Er wordt aangetoond dat een CDR gebaseerd op een fase vergrendelende lus (PLL), het gunstigste type is voor de hogesnelheidoptische communicatie. Hoewel dit type nog enkele minpunten heeft, kunnen ze weggewerkt worden door de toepassing van digitale PLL-technieken. Maar in de praktijk worden deze technieken zelden toegepast in een CDR, omdat enkele uitdagingen nog steeds verhinderen dat de digitale technieken hun volledige potentieel kunnen bereiken. Deze uitdagingen worden in kaart gebracht en mogelijke oplossingen worden voorgesteld. Dit zal uiteindelijk leiden tot de volgende generatie van de hogesnelheids- en laagvermogen kloken-data-extractie die digitaal zal zijn of met andere woorden een volledig gedigitaliseerde klok-en-data-extractie.

In Hoofdstuk 3 wordt de niet-lineaire werking van de CDR onderzocht door gebruik te maken van beschrijvende functietechnieken in het fasedomein. Ten eerste worden de stabiliteit en de faseruis van een analoge ladingspomp CDR besproken. Vervolgens wordt het fasemodel uitgebreid om een representatief model voor een volledig gedigitaliseerde klok-en-data-extractie (AD-CDR) te vormen. Dit model laat toe om de totale faseruis en de robuustheid tegen lange inactieve sequenties te onderzoeken. Ter afronding van dit hoofdstuk worden de simulatieresultaten besproken.

Een overzicht van het ontwerp van de voorgestelde AD-CDR-schakeling wordt weergegeven in Hoofdstuk 4. Het hoofdstuk start met de architectuur van het systeem, waarbij vervolgens wordt overgegaan tot een diepgaande studie van de belangrijkste bouwblokken. Hierbij hoort ook de uitgebreide vergelijkende studie tussen de conventionele en de onlangs voorgestelde Inverse Alexander fasedetector (PD).

Hoofdstuk 5 bespreekt de applicatie-specifieke geïntegreerde schakeling (ASIC) implementatie van een AD-CDR in een 40 nm laagvermogen CMOS technologie. De beschrijving begint met de globale indeling en achtereenvolgens wordt de implementatie van elk onderliggend bouwblok in detail

besproken.

Om de correcte werking en het lage energieverbruik te demonstreren, werden metingen uitgevoerd. Deze worden besproken in Hoofdstuk 6.

Het laatste hoofdstuk (Hoofdstuk 7) geeft een overzicht van de belangrijkste conclusies van het uitgevoerde onderzoek weer.

Ten slotte zijn de berekeningen van de lineaire tijdsvariante (LTV) analyse van het volledig gedigitaliseerde klok-en-data-extractie model in Appendix A opgenomen.

xxxii

### **English Summary**

During the last couple of years, data traffic has been rising exponentially and it is predicted that this growth is not going to end anytime soon. This is due to new broadband applications in the field of entertainment, commerce, industry, health care and social interactions which demand increasingly higher data rates and quality of the networks and Information and Communications Technology (ICT) infrastructure. In addition, high definition video streaming and cloud services will continue to push the demand for bandwidth.

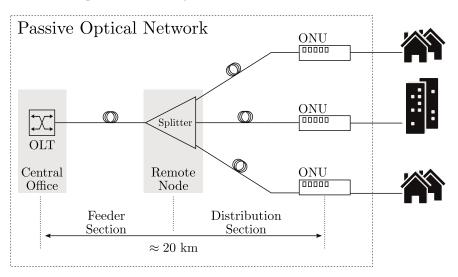

In the current architecture of the internet, end-users connect to the public network using the access network of an internet service provider. Today, this access network uses Passive Optical Network (PON) technologies because optical fiber is highly energy efficient for high data rates. Still, research has shown that the power consumption of communication networks is taking up a significant and growing share of the total global power consumption. Therefore, over the past few years, a stronger awareness has risen with respect to this negative environmental impact of massive power consumption in communication networks.

This has led to the foundation of the GreenTouch consortium in 2010, which focuses on the problem of increasing data rates while reducing the economical and environmental impact. Its mission is to show that the energy efficiency of communication networks could be improved by a factor of  $1000 \times$  by 2020, compared to the GreenTouch-defined baseline network which was built using the most energy efficient equipment available in 2010.

An important part of an optical receiver in a PON access network are Clock and Data Recovery (CDR) circuits. These CDR circuits are currently implemented with bulky and power hungry analog sub-blocks and thus have a lot of room for improvement. In this dissertation, low-power subsampling All-Digital Clock and Data Recovery (AD-CDR) techniques are presented as an answer to the various challenges next-generation networks are facing. To demonstrate this, a 25 Gb/s Phase Locked Loop (PLL)-based All-Digital Clock and Data Recovery (AD-CDR) circuit prototype was implemented in an advanced CMOS technology (40 nm).

Thanks to the highly digital architecture, the active die area is very compact and only occupies  $0.050 \text{ mm}^2$  which is significantly smaller than competing work. The power efficiency of the CDR core is 1.8 pJ/b which is also better than the state-of-the-art. Additionally, the All-Digital Clock and Data Recovery (AD-CDR) is highly adaptable: i.e. the characteristics of the loop filter can be tuned to satisfy multiple jitter tolerance specifications. Moreover, the operating range can be varied from 12.5 Gb/s to 25 Gb/s, which is the broadest operating range of any digital CDR that does not use a highquality, multi-gigahertz reference clock. Due to the truly digital frequency adaptable nature, the power consumption decreases linearly with the data rate and hence an excellent power efficiency is maintained over the entire operating range: e.g. at 25 Gb/s the power consumption is 46 mW while at 12.5 Gb/s this is 23 mW.

Furthermore, the AD-CDR is also able to capture burst mode data. The burst mode operation of the CDR is realized thanks to the lack of frequency drift between bursts and the possibility to adapt the Digital Loop Filter (DLF) parameters to obtain a large loop bandwidth. These features enable short settling times. As a result, the AD-CDR does not require a high-accuracy reference clock nor a start-of-burst signal. Only the Digitally Controlled Oscillator (DCO) needs a 1-time only calibration to ensure that its frequency is in the vicinity of the line rate. This significantly simplifies the integration of the component in a system.

The dissertation is composed of seven chapters and one appendix: Chapter 1 discusses the impact of increasing data rates and the desire to reduce power consumption in communication networks. Subsequently, the current core-metro-access architecture is presented and typical numbers are given to show why the power consumption of the access tier constitutes the lion's share of the total power consumption due to the vast amount of devices in the network. The access network is discussed, including the evolution to all-optical access networks and the concept of PONs.

Chapter 2 introduces CDR circuits and highlights the importance of these circuits. Additionally, the performance measures and a brief overview of different CDR types are given. A PLL-based CDR proves to be the most favorable type for high speed optical communication systems. Although this type still has some drawbacks, they can be overcome by using digital

PLL techniques. However, in practice these techniques are rarely implemented in a CDR because there are still some challenges that prevent the digital PLL techniques from reaching their full potential. These challenges are identified and solutions are proposed. This leads to a next-generation of high-speed and low-power Clock and Data Recovery circuits which will be digital, i.e. an All-Digital Clock and Data Recovery (AD-CDR).

In Chapter 3, the non-linear operation of the CDR is investigated using describing function techniques in the phase domain. First, the stability and the phase noise are discussed for the case of an analog charge pump CDR. Next, the phase domain model is extended to the case of the proposed AD-CDR. The phase noise and the robustness against long idle sequences are investigated. Finally, simulation results are discussed.

An overview of the design of the proposed AD-CDR circuit is given in Chapter 4. It starts with the system architecture and is followed by an in-depth discussion covering the most critical building blocks. This also includes an elaborate comparison between the conventional and the newly proposed Inverse Alexander Phase Detector (PD).

Chapter 5 discusses the implementation of an AD-CDR Application Specific Integrated Circuit (ASIC) in a 40 nm Low Power CMOS technology. The top-down approach starts with the description of the top-level implementation. Subsequently, the implementation of each building block is covered in detail.

To demonstrate the correct operation and low power efficiency, measurements were performed and are presented in Chapter 6.

The final chapter (Chapter 7) provides an overview of the foremost conclusions of the presented research.

Finally, the calculations of the Linear Time-Variant (LTV) analysis of the AD-CDR model are included in Appendix A.

#### List of Publications

#### **Publications in International Journals**

- M. Verbeke, P. Rombouts, H. Ramon, J. Verbist, J. Bauwelinck, X. Yin and G. Torfs, A 25 Gb/s All-Digital Clock and Data Recovery Circuit for Burst Mode Applications in PONs [Invited], Journal of Lightwave Technology, Pre-print, DOI:10.1109/JLT.2017.2784848, pp. 1-7, December 2017.

- M. Verbeke, P. Rombouts, H. Ramon, B. Moeneclaey, X. Yin, J. Bauwelinck and G. Torfs, *A 1.8-pJ/b, 12.5-25-Gb/s Wide Range All-Digital Clock and Data Recovery Circuit*, IEEE Journal of Solid-State Circuits, Pre-print, DOI: 10.1109/JSSC.2017.2755690, pp. 1-14, October 2017.

- **M. Verbeke**, P. Rombouts, X. Yin and G. Torfs, *Inverse Alexander phase detector*, Electronics Letters, vol. 52, no. 23, pp. 1908-1910, October 2016.

- A. Vyncke, G. Torfs, C. Van Praet, **M. Verbeke**, A. Duque, D. Suvakovic, H.K. Chow and X. Yin, *The 40 Gbps cascaded bit-interleaving PON [Invited]*, Optical Fiber Technology, vol. 26, part A, pp. 108-117, December 2015.

- M. Verbeke, P. Rombouts, A. Vyncke and G. Torfs, *Influence of Jitter on Limit Cycles in Bang-Bang Clock and Data Recovery Circuits*, IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 6, pp. 1463-1471, June 2015.

#### **Publications in International Conferences**

• M. Verbeke, P. Rombouts, H. Ramon, G. Torfs, J. Bauwelinck and X. Yin, A 25 Gb/s all-digital clock and data recovery circuit for burst

*mode applications in PONs [Highly ranked paper]*, the 43rd European Conference on Optical Communication (ECOC 2017), Gothenburg, Sweden, September 2017.

- **M. Verbeke**, P. Rombouts, A. Vyncke and G. Torfs, *Influence of Jitter on Limit Cycles in Bang-Bang Clock and Data Recovery Circuits [TCAS Special]*, IEEE International Symposium on Circuits and Systems (ISCAS 2016), Montreal, Canada, May 2016.

- A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, A Low Power 40 Gbit/s Cascaded Extension to Bit-interleaving Optical Networks Enabling Next-generation Metro/access Connectivity, 20th Annual Symposium of the IEEE Photonics Society Benelux Chapter, Brussels, Belgium, November 2015.

- A.Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, and A. Duque, *Voltage controlled oscillators for 40Gbit/s cascaded bit-interleaving PON*, Advances in Wireless and Optical Communications (RTUWO 2015), Riga, Latvia, November 2015.

- A. Vyncke, G. Torfs, M. Verbeke, and X. Yin, An 8-phase 10 GHz Voltage Controlled Ring Oscillator for 40 Gbit/s BiPON Clock-anddata Recovery, 11th Conference on PhD Research in Microelectronics and Electronics (IEEE PRIME 2015), Glasgow, United Kingdom, July 2015.

- A.Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, *CBI-PON: a Low Power Solution Offering Flexible Bandwidth Allocation for 40 Gbit/s Next Generation Metro/access Networks*, IEICE Information and Communication Technology Forum 2015 (ICTF 2015), Manchester, United Kingdom, June 2015.

- X. Yin, H. Chow, A. Vyncke, D. Suvakovic, G. Torfs, A. Duque, D. Van Veen, M. Verbeke, T. Ayan, and P. Vetter. *CBI: a Scalable Energy-efficient Protocol for Metro/access Networks [Invited]*, 2014 IEEE Online Conference on Green Communications (OnlineGreen-Comm), November 2014.

- G. Torfs, X. Yin, A. Vyncke, M. Verbeke, and J. Bauwelinck. Solutions for a Single Carrier 40 Gbit/s Downstream Long-reach Passive

*Optical Network*, 2014 16th International Telecommunications Network Strategy and Planning Symposium (Networks 2014), September 2014.

#### **Publications in National Conferences**

• M. Verbeke, Fast determination of instability in a non-linear Clock and Data Recovery circuit, 16th FEA PhD symposium, December 9, 2015, Ghent, Belgium

#### **Chapters in Books**

A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, *Design and measurement of VCOs for 40Gbit/s Cascaded Bit-Interleaving PON*, 1st International IEEE Conference on Advances in Wireless and OPtical Communications 2015, Latvia, Riga, November 2015. Riga: RTU Press, 2015, pp. 91-104. ISBN 978-9934-10-758-0

### Part I

## Introduction to Internet Communication and CDRs

# Introduction

#### **1.1 Evolution of Data Consumption**

#### **1.1.1 Internet Traffic**

In 1995, less than 1% of the world population had an internet connection. Since then the number of internet users has increased tremendously: from 1999 to 2013, the number of internet users increased tenfold and reached the first billion of internet users in 2005. Today, there are over 3 billion internet users (Fig. 1.1), which corresponds to around 40% of the world population [1].

Over the last decades, not only the number of internet users, but also the data traffic, as well as the internet access speed have increased enormously and are still growing. It is expected that the global average broadband speed will nearly double from 2016 to 2021 (from 27.5 Mb/s to 53.0 Mb/s) [2]. This broadband speed is a crucial enabler of internet traffic, because broadband-speed improvements result in an increased consumption and the use of high-bandwidth content and applications.

Fig. 1.2 shows a prediction of the evolution of the major applications of future global internet traffic. The application that generates and will generate the most of global internet traffic is video. Video continues to be of enormous demand in today's home and this can be seen by observing the evolution of the number of Netflix subscribers (Fig. 1.3). Also profound

Figure 1.1: The number of internet users from 2001 until 2017 [3].

Figure 1.2: The future global internet traffic by application [2].

functionalities such as virtual reality, augmented reality, immersive video and video surveillance are emerging. This traffic type is a high-bandwidth consuming application and can cause significant new network design implications. For example, traffic associated with virtual and augmented reality applications is anticipated grow 20-fold by 2021, while video surveillance accounts will grow 15-fold by 2021 [2].

This growth in traffic is also more pronounced due to the significant bandwidth demands of the video application requirements of the future such as Ultra-High-Definition (UHD) streaming, 8K wall TV, UHD virtual reality. In Fig. 1.4, a scenario with video applications of the future is explored: today's bandwidth needs are only a tiny piece of the future needs [2]. It shows that the bit rate for a 8K wall TV at about 100 Mb/s is only one fifth of the need for UHD virtual reality (VR). It is estimated that by 2021 more than half (56 %) of the installed flat-panel TV sets will be UHD, compared to 15 % in 2016 [2]. In total, the sum of all forms of IP video, which includes internet video, IP VoD, video files exchanged through file sharing, video-streamed gaming, and video conferencing, will continue to be in the range of 80 to 90 % of the total internet traffic [2].

Next to internet video, there are some emerging contributors of the future data consumption (e.g. gaming, file sharing and web/data) that do not have a big relative share of the future global internet traffic (Fig. 1.2). However, the absolute value of internet traffic they produce is increasing rapidly.

For the case of internet gaming, the traffic will grow nearly tenfold between 2016 and 2021. Gaming on demand and streaming gaming platforms have been in development for several years, with many newly released in the last couple of years. While graphical processing is performed locally on the gamer's computer or console for traditional gaming, the game graphics for cloud gaming are produced on a remote server and transmitted over the network to the gamer. As cloud gaming becomes popular, gaming could have an increasing impact on the future internet traffic [2].

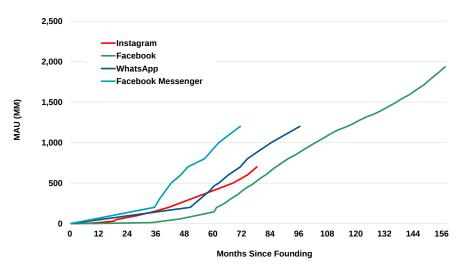

As social networking is one of the most popular ways for online users to spend their time, it is only natural that the number of social network users is also increasing. Fig. 1.5 illustrates the spectacular augmentation in Facebook platform medium attachment units for Instagram, Facebook, WhatsApp and Facebook Messenger since their launch. Despite Facebook being the absolute market leader in terms of medium attachment units, other social networks have thrived nonetheless. Some social networks such as LinkedIn have specialized in professional networking, whereas others such as Chinese-language Qzone or Renren support huge local audiences [5].

Netflix Subscribers (MM) & Quarterly Revenue (\$MM), 2/99 – 3/17, Global Q1:17 Streaming ARPU per Month = \$9.14

Figure 1.3: The evolution of the Netflix subscribers [4].

Figure 1.4: The current and future video requirements [2].

Currently, there are more than 1.6 billion social network users worldwide (about 64% of internet users) and these figures are expected to grow [5]. A wide selection of social networks also heavily relies on user-generated content<sup>1</sup>, increasing the need for more bandwidth.

Facebook Platform MAUs, Global, Months Since Launch

Figure 1.5: The evolution of Facebook platform Medium Attachment Units (MAUs) [4].

#### 1.1.2 Power Consumption

In this evolution of internet traffic, the cost and especially the power consumption of the enabling electronic circuits are important aspects. The global Information and Communications Technology (ICT) industry accounts for approximately 2% of global carbon dioxide (CO<sub>2</sub>) emissions, which is the same figure for the global airline industry [6, 7]. Additionally, with respect to the total worldwide electricity consumption, the relative share of the ICT electricity consumption has increased from about 3.9% in 2007 to 4.6% in 2012 [7].

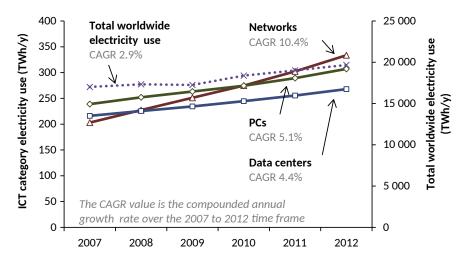

Fig. 1.6 highlights the importance of networks in the electricity consumption of ICT: the total worldwide electricity consumption in communication networks has increased from 219 TWh per year in 2007 to 354 TWh per

<sup>&</sup>lt;sup>1</sup>Image-heavy Tumblr, Instagram and Pinterest are focused on content-creating.

year in 2012 [8]. This corresponds to an annual growth of about 10%. When we compare this to the total worldwide electricity consumption [9], we see that the share of networks is becoming increasingly important. Where communication networks only consumed about 1.3% of worldwide electricity in 2007, their relative contribution has increased to 1.8% in 2012 [8]. The electricity consumption in communication networks is thus growing at a faster pace ( $\approx 10\%$  in the interval 2007-2011) than the overall electricity consumption ( $\approx 3\%$  in the interval 2007-2011) [10]. These results and the fact that data rates and subscription numbers will most likely continue to grow in the following years, make it both essential for the industry and extremely challenging to cope with the increasing demand [11]. Therefore, in recent years, the energy efficiency of communication networks has received a lot of research attention: there are advances in circuit architecture, interconnect topologies, and transistor scaling [11].

Figure 1.6: The Compound Annual Growth Rate (CAGR) of the electricity consumption in ICT compared to the total worldwide electricity consumption. Networks is the fastest growing category [12].

#### **1.2 Networks Today**

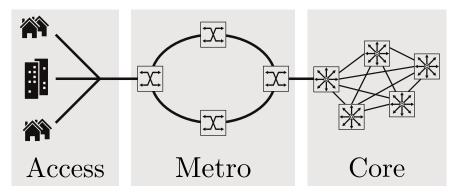

Modern telecommunication networks are constructed as a three-level hierarchical network (Fig. 1.7), where each level is called a tier [13]. Each tier can roughly be identified with a geographical entity. The core tier, which typically uses a mesh topology, is responsible for interconnecting continents and countries, spanning distances ranging from hundreds to thousands of kilometers.

Figure 1.7: The modern telecommunication network hierarchy [14].

The metro tier corresponds to a metropolitan area, and can roughly be seen as the area a large city covers. Metro networks consist of a ring topology interconnecting several central offices over tens to hundreds of kilometers.

The access tier is the lowest level and provides connectivity to the end-user. Access networks are designed to operate on distances of a few kilometers to tens of kilometers. Contrary to the core and metro tier, the access tier is deployed in a variety of configurations, such as bus, star or ring topologies.

Due to the hierarchical construction of a modern telecommunication network, it is clear the amount of network devices deployed in the access tiers far outnumbers those in the core tiers. Table 1.1 reveals a projection of the power consumption, split in terms of core, metro and access network and customer premises equipment, by 2015-2020 assuming a business-as-usual scheme. It can be seen that small power consumption reductions in access network devices potentially have a much bigger impact on the complete system than high power consumption reductions in power-hungry devices in the core network.

#### 1.2.1 Optical Access Networks

While the core and metro networks incorporate optical fibers, an access network historically uses copper cable. This is because the twisted pair telephone cable network and the coaxial cable TV networks were readily available when the access networks had to be deployed [14, 16]. However, as the bandwidth demand has accelerated and as electrical channel

|        | Power consumption | Number of  | BAU      |

|--------|-------------------|------------|----------|

|        | (W/device)        | devices    | (GWh/yr) |

| Home   | 10                | 17 500 000 | 1 533    |

| Access | 1 280             | 27 344     | 307      |

| Metro  | 6 000             | 1 750      | 92       |

| Core   | 10 000            | 175        | 15       |

Table 1.1: An Italian network forecast (2015-2020): device density and energy requirements in the Business-As-Usual (BAU) case [15].

impairments become increasingly severe with the rise of data rates, optical interconnects have become an increasingly attractive alternative to traditional electrical wireline interconnects in access networks. The advantages of using optical interconnects are summarized in Table 1.2.