Speeding Up Architectural Simulation through High-Level Core Abstractions and Sampling

Versnellen van architecturale simulatie via abstracte prestatiemodellen en bemonstering

Trevor Carlson

Promotor: prof. dr. ir. L. Eeckhout Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2013 - 2014

ISBN 978-90-8578-698-6 NUR 958 Wettelijk depot: D/2014/10.500/44

### Acknowledgements

Over the years, I have always been very interested in discovering new things. When I was a child, I assumed that I could build electronics that did fancy things just by drawing a schematic on paper. I enjoyed thinking about devices that I could build that would change the way that things worked. Throughout my career, I found that discovering new and interesting ideas and directions was my true passion. I am thankful that both my mother and father have always been supportive of me, allowed me to be creative, and allowed me to make mistakes. During my younger years at school, my Junior High Technology teacher, David Rockett, gave me the freedom to experiment with new ideas, program robots and build trains that used magnetic levitation. Later on, when working for IBM, I realized that I still have this passion and I worked to file four patents as a sideproject to my normal work, not even dreaming at the time that it would allow me to start a path towards completing a Ph.D. Solving difficult problems allowed me to think in new ways and better understand my personal limitations. Of course, I wanted to move past these limitations at each chance that I could get, but I also understood that hard-work was required. I will never be done proving myself, and I will always be challenged to accomplish something that others might feel is too difficult to solve.

My Ph.D. would not have been possible if it was not for my original manager at IMEC, Bjorn De Sutter, who saw that I could make the transition from industry to academia. My advisor, Lieven Eeckhout was instrumental in helping me better understand how to become a better researcher. Lieven's advice, support and constant encouragement to do even better have helped me learn how to conduct research in an academic setting while learning from experts in the field. Without his guidance and insight, I would not be where I am today.

Looking back at the time that I spent at the university, I was very happy that two things occurred at just the right time. First, the founding of the ExaScience Lab gave my Ph.D. a new direction. The focus of the lab allowed me to zero in on the needs of High Performance Computing, both from a hardware and software perspective. To accomplish this, we felt that faster simulation methodologies could help us improve the state of the art. At the same time, Wim Heirman joined our group to help us realize our goal of faster simulation. From one of our very first meetings, I saw that our collaboration had great promise. We sat down to sketch out the ideas for what would become general-purpose time-based multi-threaded sampling, published two years and tens of thousands of simulations later. At the time, I did not realize that it was going to be both an enjoyable and fruitful period, both professionally and personally. Together with Wim's help and guidance, we have been able to accomplish much more than I had envisioned.

My wife, Stephanie, took a chance on me as I moved back into academia and I started my Ph.D.; I had already been working for more than 6 years in industry. While difficult, she saw that it could be a rewarding experience if I could stay focused, complete all tasks early, and above all, enjoy the work that I was doing. She has been there every step of the way, making delicious baked goods, helping to proof-read articles, and supporting me through the many difficult times where it appeared that no hope was in sight. Thankfully, I have enjoyed every minute of my Ph.D., and only hope I will continue to be challenged throughout life. I might not have been the one who accomplished everything early, but I do feel that I have been able to accomplish everything, if not more, that I set out to do.

> Trevor E. Carlson Ghent, June 11th, 2014

## **Examination Committee**

- Prof. Jan Van Campenhout, voorzitter Vakgroup ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. Lieven Eeckhout, promotor Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. Koen De Bosschere Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Stijn Eyerman, secretaris Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Ayose Falcon Intel Barcelona Research Center Spain

- Prof. Jan Fostier Vakgroep INTEC, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Wim Heirman Intel ExaScience Lab Leuven

- Prof. Thomas Wenisch University of Michigan, Advanced Computer Architecture Lab USA

iv

## **Reading Committee**

- Dr. Stijn Eyerman Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Ayose Falcon Intel Barcelona Research Center Spain

- Prof. Jan Fostier Vakgroep INTEC, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Wim Heirman Intel ExaScience Lab Leuven

- Prof. Thomas Wenisch University of Michigan, Advanced Computer Architecture Lab USA

vi

## Summary

Both Moore's Law and Dennard Scaling have allowed us to make large improvements in chip density, energy efficiency and performance over the last 20 to 30 years of microprocessor design. Moore's Law predicts that the number of transistors in a processor will double every two years, and Dennard Scaling states that power density remains constant because of transistor scaling. While Dennard Scaling is seen as now coming to an end, Moore's Law, by predicting the continued growth in the number of available transistors, continues to provide us with opportunities to enhance the speed and efficiency of future microprocessors.

Through Pollack's Rule, we see that a single, large processor will not allow us to improve performance without a large increase in the complexity of current CPU core designs. Pollack's Rule states that the performance due to microarchitectural advancements improves with the square root of the complexity, or area used. This means that using a larger and larger area for a single, monolithic processor results in diminishing returns with respect to improved processor performance. The multi- and many-core era has allowed us to continue to scale the performance of our platforms through the use of many efficient cores instead of a single, less efficient one. On the horizon, we expect this trend to continue with systems utilizing larger numbers of cores. Higher processing requirements go hand-in-hand with larger on-chip caches that are required to sustain processor bandwidth requirements. Processor pin density limitations make it very difficult to increase the bandwidth to the processor, requiring larger caches to reduce bandwidth requirements, maintaining high performance.

These processor trends directly affect the ability to simulate improved architecture designs on today's hardware. As core complexity, core count and on-chip cache size increase, so do the simulation requirements needed to evaluate the performance of these microarchitectures. This is because both greater numbers of cores and more complex cores require additional modeling steps (and therefore additional simulation time) to evaluate. Larger caches tend to translate into longer simulation times as well, because they can require higher instruction counts to exercise the entire cache. Unfortunately, while Pollack's Rule has shown us a path to improve application performance through multi-core microarchitectures, simulation design technologies have not adapted to the changing environment. Typical microarchitecture simulators are single-threaded and therefore will not continue to improve their performance with newer microarchitectures. This situation presents an increasing simulation gap, where simulators will not be able to continue to scale with microarchitectural improvements while the requirements for simulation will continue to grow.

These growing simulation requirements and the simulation gap require unique solutions to allow architects and designers to continue to advance the state of the art in microarchitectural design. In this work, we propose a number of approaches to directly counter these trends by reducing the simulation time required for design exploration. We do this through two orthogonal approaches. First, we improve the speed of the simulator directly, allowing for the same amount of work to be done in a shorter time. We do this by using high-level abstraction models to provide faster simulation speeds. Second, through application sampling, we reduce the application into a smaller, representative sample, reducing the amount of work that the simulator needs to perform.

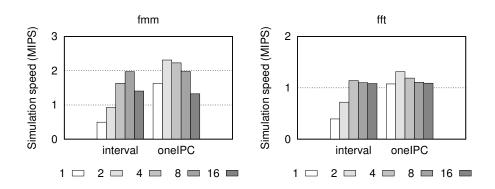

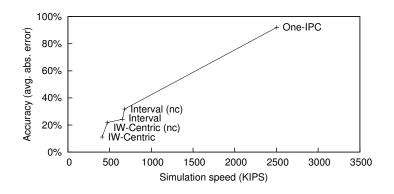

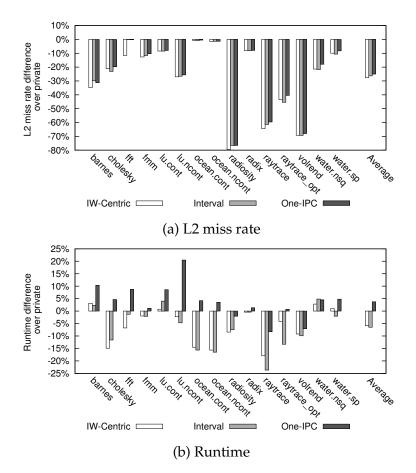

Speeding-up Simulation While detailed cycle-accurate simulation methodologies have been used for both discovering and validating microarchitectural improvements, changing the simulator to use higher abstraction levels for microprocessor simulation is one way to alleviate the increasing simulation demands resulting from Moore's Law. In this work, we developed a new microarchitectural simulator, the Sniper Multi-Core Simulator, to show that higher abstraction levels, with respect to core, cache and memory hierarchy and simulation infrastructure models, can provide good accuracy with higher simulation speeds. As we demonstrate, naive, simple core models can produce inaccurate results, both from an absolute and relative perspective. But using more intelligent, mechanistic high-level models can result in high accuracy at very high speeds. More specifically, we demonstrate that high-level abstractions can accurately predict both performance and trends, with average errors starting at 11.1% with aggregate speeds of up to 2.0 MIPS. In addition, we show that while very simple models, such as the one-IPC core simulation models, provide faster simulator performance, they do not necessarily allow one to draw the same conclusions as both the original hardware and more accurate models provide. We find core models that honor both instruction-level parallelism (ILP) and memory-level parallelism (MLP), such as those used in interval simulation, allow for more accurate simulation results.

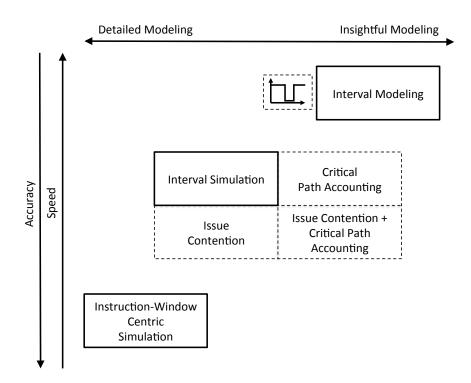

In addition to interval simulation, we want to allow architects to have access to additional points in the accuracy vs. simulation speed trade-off curve where improved accuracy can help for additional refinement as necessary for late-phase validation. We first enhance the original interval simulation model with features such as issue contention modeling to enable higher accuracy with minimal slowdown. We show that these features can get us closer to a more accurate simulation compared to hardware. In addition to interval simulation improvements, we present a novel processor core model called the instruction-window centric model, that allows for fine-grained analysis and timing control with a modest slowdown in simulation speed. The instruction-window centric processor core models improve average error from 24.3% to 11.1% for single-core models. Finally, we demonstrate the speed-versus-accuracy trade-offs across a number of benchmarks to provide a detailed overview of how these different models can provide the architect with different options for exploration or detailed analysis.

**Application Reduction through Sampling** There are two orthogonal approaches to speeding up simulation. The first approach, discussed in the previous paragraph, speeds up the simulator itself, providing a faster result given a fixed amount of work. Sampling is a well-known technique that is orthogonal to speeding up the simulator itself, and is used to reduce the amount of work to be the simulated. This is done by taking advantage of inherent application similarity that occurs naturally in most applications because of looping and other common programming constructs. Single-threaded application sampling has been studied extensively and is considered to be mature. Nevertheless, multi-threaded application sampling poses new challenges. Now, thread interaction and timing needs to be taken into account, either in shared microarchitectural structures, like shared caches, or when looking at thread ordering and other concerns caused by dynamic scheduling, such as through work-stealing.

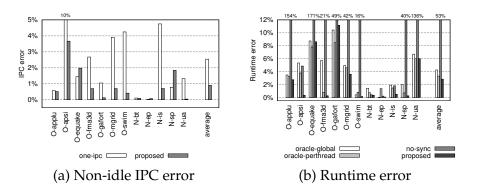

In this thesis, we present two advances in the field of multi-threaded application sampling. First, we present a generic time-based sampling approach that solves many of the issues inherent to multi-threaded application sampling for synchronizing threads. We show that taking into account per-thread IPCs as well as properly handling inter-thread interactions during fast-forwarding significantly increases sampling accuracy. In addition, we show that application phase behavior needs to be taken into account when selecting appropriate regions. With our methodology, we simulate less than 10% of the application in detail, while maintaining a low average error of 3.5%.

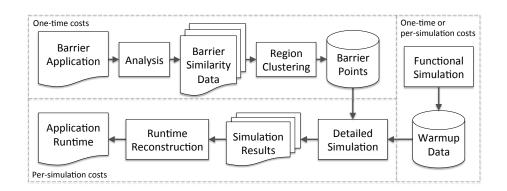

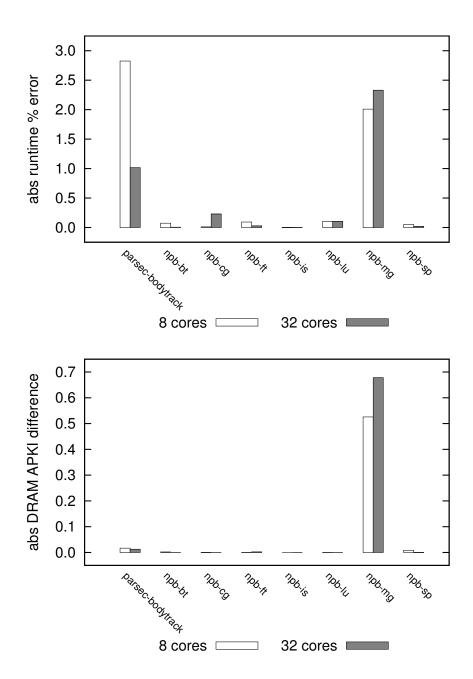

In addition to the general case of multi-threaded sampled simulation, we improve sampled simulation for an important subset of multi-threaded applications, namely, barrier-based applications. We propose new methods for the identification and characterization of inter-barrier regions for the purpose of application similarity analysis and reduction. Using these new similarity methods, we propose a methodology for clustering regions to allow one to select corresponding representative regions of interest. Finally, we evaluate this methodology on simulated 8- and 32-core machines and find an average reduction of resources by  $78 \times$ . We demonstrate low average errors, of 0.9%, with a speedup factor of  $24.7 \times$  on average and a maximum of  $866.6 \times$ .

## Samenvatting

Dankzij de wet van Moore en Dennards schalingswet zijn we erin geslaagd grote verbeteringen in de chipdichtheid, energie-efficiëntie en prestatie te bereiken. Volgens de wet van Moore verdubbelt het aantal transistors op een chip elke twee jaar; Dennards schalingswet stelt dat de vermogendichtheid constant blijft vanwege transistorschaling. Terwijl Dennards schalingswet ten einde loopt, blijft de wet van Moore geldig, wat tot een bijzonder grote uitdaging leidt teneinde de prestatie en efficiëntie van toekomstige processors blijvend te verbeteren.

Op basis van de wet van Pollack, die stelt dat de complexiteit kwadratisch toeneemt als functie van de beoogde prestatieverbetering, zien we dat een grotere processor ons niet zal toelaten de prestatie verder te verbeteren zonder een aanzienlijke toename in complexiteit. De wet van Pollack, in combinatie met de wet van Moore en het einde van de schaling volgens Dennards schalingswet, heeft geleid tot het multi-core tijdperk waarbij meerdere processorkernen samen geïntegreerd worden op één chip, en waarbij software geparallelliseerd dient te worden teneinde prestatieverbetering te bereiken. Er wordt algemeen verwacht dat het aantal processorkernen per chip zal blijven toenemen in de nabije toekomst. Een stijgend aantal processorkernen in combinatie met een beperkt aantal externe pinnen, leidt tot steeds grotere caches teneinde de processorkernen tijdig van data te kunnen voorzien gezien de beperkte geheugenbandbreedte.

Deze trends in processorontwerp hebben een grote invloed op het ontwerpproces en meer specifiek de simulatie van toekomstige processors. Een stijgend aantal processorkernen en steeds grotere caches verhogen de complexiteit van de simulator, en hebben derhalve een negatieve impact op de simulatietijd. Bovendien zijn de meeste hedendaagse simulators enkeldradig waardoor de simulatiesnelheid niet aanzienlijk zal toenemen in de komende jaren. Dit leidt tot een simulatiekloof: simulators schalen niet mee met de architecturen die zij dienen te simuleren.

In dit werk stellen we een aantal oplossingen voor voor het versnellen van de architecturale simulatie van multicore processors. We doen dit op twee manieren. Eerst verbeteren we de simulatiesnelheid door het abstractieniveau van modellering te verhogen. Ten tweede reduceren we de te simuleren werklast m.b.v. bemonstering. Simulatieversnelling. In dit werk beschrijven we Sniper, een parallelle architecturale simulator die de simulatie aanzienlijk versnelt door het modelleren van de processorkernen op een hoger abstractieniveau, zonder aan al te veel nauwkeurigheid in te boeten. We gebruiken hiertoe een analytisch, mechanistisch prestatiemodel van de processorkern, dat leidt tot een hoge nauwkeurigheid en hoge simulatiesnelheden. Onze experimentele resultaten geven aan dat hoog-niveau prestatiemodellen een gemiddelde afwijking kunnen behalen van 11% ten opzichte van echte hardware, en dit aan een simulatiesnelheid tot 2 MIPS (miljoen instructies per seconde)—2 tot 3 grootteordes sneller dan gedetailleerde architecturale simulatie. Bovendien tonen wij aan dat ofschoon heel eenvoudige modellen, zoals het veel gebruikte 'one-IPC' processorkernsimulatiemodel, sneller zijn, zij niet de benodigde nauwkeurigheid behalen. Nauwkeurige simulatie vereist de modellering van instructie-niveauparallellisme (ILP) en geheugen-niveauparallellisme (MLP), zoals aangeleverd in het intervalmodel. Naast verbeteringen tot het intervalmodel teneinde de structurele hazards nauwkeuriger te modelleren, presenteren we eveneens een nieuw processorkernmodel, namelijk het instructievenstersimulatiemodel, dat de prestatie van de processorkern modelleert door enkel te focussen op de werking van het instructievenster, de centrale eenheid van een hedendaagse superscalaire processor. Het eindresultaat van deze studie is een aantal hoog-niveau simulatiemodellen met een waaier aan mogelijkheden qua nauwkeurigheid versus simulatiesnelheid.

**Werklast Reductie door Bemonstering.** Bemonstering is een gekende techniek om de te simuleren werklast te reduceren, teneinde op die manier de simulatietijd in te korten. Terwijl bemonstering van enkeldradige applicaties een mature en veelvuldig gebruikte techniek is, is de bemonstering van meerdradige applicaties een openstaand onderzoeksvraagstuk. Bemonstering van meerdradige applicaties wordt bemoeilijkt door de onderlinge interacties tussen de draden via synchronisatie en gedeelde hulpbronnen in de hardware.

In dit werk presenteren we twee technieken voor het bemonsteren van meerdradige applicaties. Tijdsgebaseerde bemonstering lost een aantal problemen op die inherent zijn aan bemonstering van meerdradige applicaties. We tonen aan dat rekening houden met de prestatie per draad alsook de inter-draadinteracties tijdens de bemonstering, de nauwkeurigheid sterk ten goede komt. Bovendien tonen we aan er bij de bemonstering rekening gehouden dient te worden met het tijdsvariërend uitvoeringsgedrag. Tijdsgebaseerde bemonstering laat toe minder dan 10% van de applicatie in detail te simuleren met een gemiddelde afwijking van 3,5% t.o.v. gedetailleerde simulatie.

De tweede bemonsteringstechniek spitst zich toe op applicaties die 'bar-

riers' gebruiken als synchronisatieprimitieve. Deze techniek laat toe representatieve inter-barrierregio's te identificeren met behulp van een microarchitectuuronafhankelijke karakterisatie van de code, gevolgd door clustering. De experimentele resultaten tonen aan de techniek leidt tot een gemiddelde afwijking t.o.v. gedetailleerde simulatie van slechts 0,9% en een gemiddelde simulatieversnelling van 24,7× (maximaal 866,6×); bovendien daalt het vereiste aantal simulatiemachines met een factor van gemiddeld 78×.

## Contents

|   | Eng        | lish Su | mmary                                                                       | vii    |

|---|------------|---------|-----------------------------------------------------------------------------|--------|

|   | Ned        | lerland | se samenvatting                                                             | xi     |

| 1 | Intr       | oductio | on                                                                          | 1      |

|   | 1.1        | Conte   | xt                                                                          | 1      |

|   | 1.2        | Challe  | enges                                                                       | 1      |

|   | 1.3        | Future  | e Simulation Requirements                                                   | 2      |

|   | 1.4        |         | ibutions                                                                    | 3      |

|   |            | 1.4.1   | Architectural Simulation                                                    | 3      |

|   |            | 1.4.2   | Application Sampling                                                        | 4      |

|   | 1.5        | Struct  | ure and Overview                                                            | 5      |

| ~ | <b>.</b>   |         |                                                                             |        |

| 2 | _          | -       | the Level of Abstraction for Scalable and Accurate Par<br>-Core Simulations | _      |

|   | 2.1        |         |                                                                             | 7<br>7 |

|   | 2.1        |         | luction                                                                     | 10     |

|   | 2.2        | 2.2.1   | ssor Core Modeling                                                          | 10     |

|   |            | 2.2.1   |                                                                             | 11     |

|   |            | 2.2.2   | One-IPC models in Graphite                                                  | 11     |

|   |            | 2.2.3   | Sniper: Interval simulation                                                 | 12     |

|   | 2.3        |         | el Simulation                                                               | 13     |

|   | 2.3<br>2.4 |         |                                                                             | 14     |

|   | 2.4        | 2.4.1   | ator Improvements       Simulator choice                                    | 15     |

|   |            | 2.4.1   |                                                                             | 15     |

|   |            | 2.4.3   | Timing model improvements                                                   | 16     |

|   | 2.5        |         | imental Setup                                                               | 18     |

|   | 2.6        | Result  |                                                                             | 10     |

|   |            | 2.6.1   | Core model accuracy                                                         | 20     |

|   |            | 2.6.2   | Application scalability                                                     | 21     |

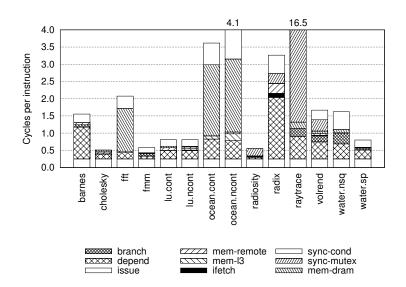

|   |            | 2.6.3   | CPI stacks                                                                  | 23     |

|   |            | 2.6.4   | Heterogeneous workloads                                                     | 24     |

|   |            | 2.6.5   | Simulator trade-offs                                                        | 25     |

|   |     | <ul><li>2.6.6 Synchronization variability</li></ul>         | 26<br>27 |

|---|-----|-------------------------------------------------------------|----------|

|   | 2.7 | Other Related Work                                          | 28       |

|   |     | 2.7.1 Cycle-level and cycle-accurate simulation             | 28       |

|   |     | 2.7.2 Sampled simulation                                    | 29       |

|   |     | 2.7.3 FPGA-accelerated simulation                           | 29       |

|   |     | 2.7.4 High-abstraction modeling                             | 30       |

|   | 2.8 | Conclusions                                                 | 30       |

| 3 |     | Evaluation of High-Level Mechanistic Core Models            | 33       |

|   | 3.1 | Introduction                                                | 33       |

|   | 3.2 | Core-level Abstractions                                     | 35       |

|   |     | 3.2.1 One-IPC Models                                        | 36       |

|   |     | 3.2.2 Interval Modeling                                     | 37       |

|   |     | 3.2.3 Interval Simulation                                   | 38       |

|   | 3.3 | Interval Simulation Improvements                            | 41       |

|   |     | 3.3.1 Functional Unit Contention Modeling                   | 41       |

|   |     | 3.3.2 Refilling the window after front-end miss events      | 44       |

|   |     | 3.3.3 Modeling of overlapped memory accesses                | 45       |

|   | 3.4 | Instruction-Window Centric Simulation                       | 46       |

|   |     | 3.4.1 Overview                                              | 47       |

|   |     | 3.4.2 Implementation Details                                | 47       |

|   | 3.5 | Evaluation and Methodology                                  | 49       |

|   |     | 3.5.1 Simulation infrastructure                             | 49       |

|   |     | 3.5.2 Hardware validation                                   | 50       |

|   |     | 3.5.3 Benchmarks                                            | 51       |

|   | 3.6 | Simulation Accuracy Comparison                              | 52       |

|   |     | 3.6.1 Absolute Accuracy Comparison                          | 52       |

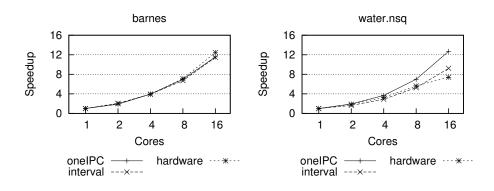

|   |     | 3.6.2 Multi-core scaling comparison                         | 53       |

|   | 3.7 | Simulation Speed Comparison                                 | 55       |

|   | 3.8 | Core model resolution affects microarchitecture conclusions | 57       |

|   | 3.9 | Conclusion                                                  | 60       |

| 4 | Sam | pled Simulation of Multi-threaded Applications              | 61       |

|   | 4.1 | Introduction                                                | 61       |

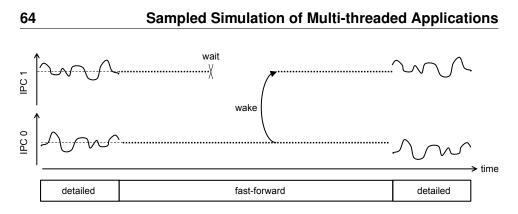

|   | 4.2 | Fast-Forwarding Parallel Applications                       | 63       |

|   |     | 4.2.1 Requirements for Accurate Parallel Fast-Forwarding    | 63       |

|   |     | 4.2.2 Accurate Multi-Threaded Fast-Forwarding               | 64       |

|   |     | 4.2.3 Comparison of Fast-Forwarding Techniques              | 65       |

|   | 4.3 | Sample Selection in Parallel Applications                   | 66       |

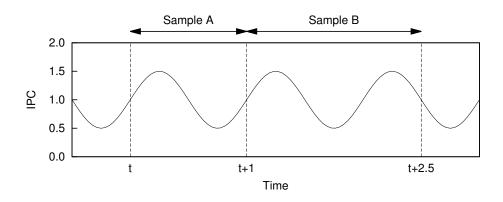

|   |     | 4.3.1 The Effect of Periodicity on Sampling                 | 67       |

|   |     | 4.3.2 Determining Application Periodicity                   | 69       |

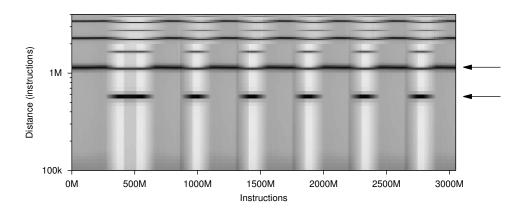

|   |     | 4.3.3 Detecting Large Application Variability over Long Pe- |          |

|   |     | riods                                                       | 71       |

|   |            | 4.3.4 Deriving Optimal Sampling Parameters                   | 72         |

|---|------------|--------------------------------------------------------------|------------|

|   | 4.4        | Experimental Setup                                           | 74         |

|   |            | 4.4.1 Simulation Configuration                               | 74         |

|   |            | 4.4.2 Implementing Sampled Simulation in Sniper              | 74         |

|   |            | 4.4.3 Selecting Sampling Parameters                          | 75         |

|   | 4.5        | Results                                                      | 76         |

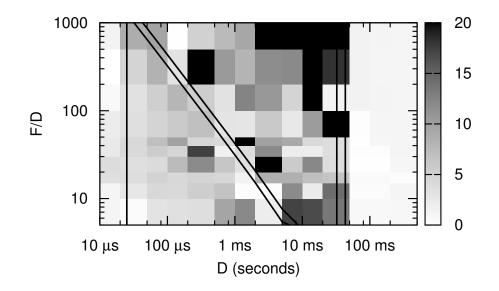

|   |            | 4.5.1 Sampling Parameter Space                               | 77         |

|   |            | 4.5.2 Predicting Optimal Sampling Parameters                 | 77         |

|   |            | 4.5.3 Random Sampling                                        | 81         |

|   |            | 4.5.4 Detailed Warmup                                        | 82         |

|   |            | 4.5.5 Potential for Simulator Speedup                        | 82         |

|   | 4.6        | Application: Architectural Exploration                       | 83         |

|   | 4.7        | Related Work                                                 | 84         |

|   |            | 4.7.1 Single-Threaded Sampling                               | 84         |

|   |            | 4.7.2 Multi-threaded Sampling                                | 85         |

|   | 4.8        | Conclusions                                                  | 86         |

|   |            |                                                              |            |

| 5 |            | rierPoint: Sampled Simulation of Multi-Threaded Applications |            |

|   | 5.1        | Introduction                                                 | 87         |

|   | 5.2        | Key Idea                                                     | 90<br>01   |

|   | 5.3        | BarrierPoint Methodology                                     | 91         |

|   |            | 5.3.1 Barrier Region Similarity Metrics                      | 92<br>04   |

|   |            | 5.3.2 Region Clustering                                      | 94<br>04   |

|   |            | 5.3.3 Detailed Region Execution                              | 94<br>05   |

|   | <b>F</b> 4 | 5.3.4 Whole-Program Runtime Reconstruction                   | 95<br>06   |

|   | 5.4        | Micro-architectural State Reconstruction                     | 96         |

|   | 5.5        | Experimental Setup                                           | 97         |

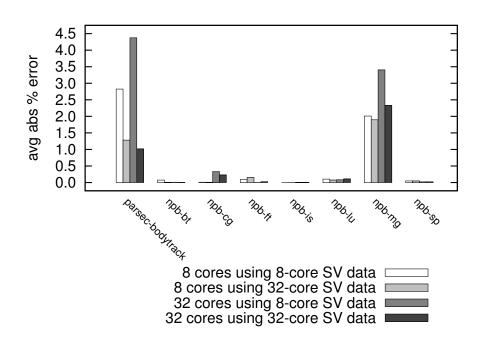

|   | 5.6        |                                                              | 102        |

|   |            | 1                                                            | 102        |

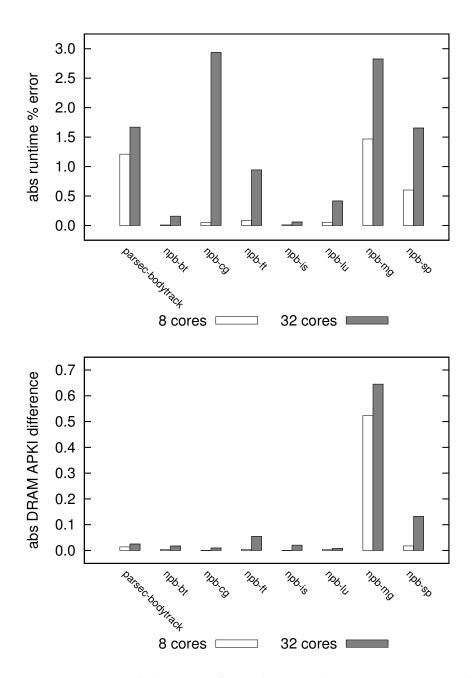

|   |            | 1                                                            | 106        |

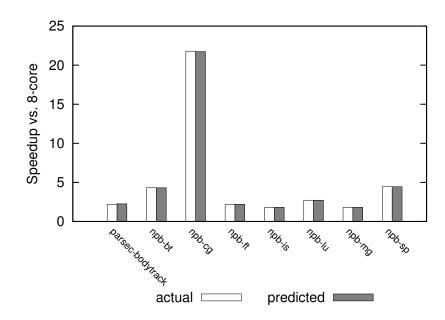

|   |            | 5                                                            | 106        |

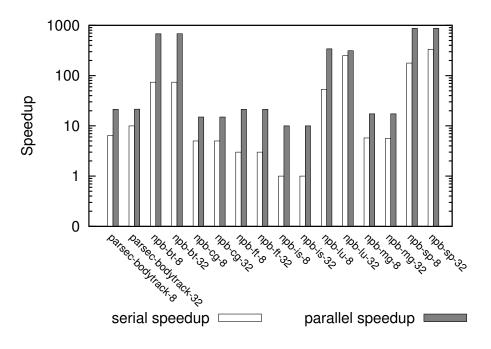

|   | 5.7        | 1 1                                                          | 106<br>107 |

|   | 5.7        |                                                              | 107        |

|   |            |                                                              | 107        |

|   |            | I O                                                          | 107        |

|   |            | 1                                                            |            |

|   |            | 1                                                            | 108        |

|   | 59         |                                                              | 109        |

|   | 5.8        | Conclusion                                                   | 109        |

| 6 | Con        | clusion                                                      | 111        |

|   | 6.1        | Overview                                                     | 111        |

|   |            | 6.1.1 Simulator Speedup with High-Level Core Models 1        | 112        |

|   |     | 6.1.2   | Worklo                     | ad Re  | edu  | ctio | n th  | nro | ug | h ] | Мı | ılti | -Th | rea | ade | ed | Sa | m | - |     |

|---|-----|---------|----------------------------|--------|------|------|-------|-----|----|-----|----|------|-----|-----|-----|----|----|---|---|-----|

|   |     |         | pling .                    |        |      |      |       |     |    |     |    |      |     |     |     |    |    |   |   | 112 |

|   | 6.2 | Future  | Work .                     |        |      |      |       |     |    |     |    |      |     |     |     |    |    |   |   | 113 |

|   |     |         |                            |        |      |      |       |     |    |     |    |      |     |     |     |    |    |   |   |     |

|   |     |         |                            |        |      |      |       |     |    |     |    |      |     |     |     |    |    |   |   |     |

| A | Add | itional | Researc                    | h      |      |      |       |     |    |     |    |      |     |     |     |    |    |   |   | 115 |

| A |     |         | <b>Researc</b><br>vare/Sof |        | e Co | -De  | esigi | n.  |    |     |    |      |     |     |     |    |    |   |   | 110 |

| A | A.1 | Hardw   |                            | ftware |      |      | ~     |     |    |     |    |      |     |     |     |    |    |   |   | 115 |

## **List of Tables**

| 2.1<br>2.2 | Simulated system characteristics for the Intel Xeon X7460<br>Benchmarks and input sets | 19<br>20 |

|------------|----------------------------------------------------------------------------------------|----------|

| 3.1        | Micro-architectural configuration                                                      | 49       |

| 3.2        | Simulator configuration options                                                        | 50       |

| 3.3        | Benchmarks and input sets                                                              | 51       |

| 3.4        | Single-core average absolute runtime errors and average ab-                            |          |

|            | solute differences for each simulation model                                           | 52       |

| 3.5        | Errors across the simulation models for different core counts.                         | 55       |

| 3.6        | Micro-architectural configuration for private and shared L2                            |          |

|            | cache configurations used for one-IPC vs. detailed core model                          |          |

|            | comparisons                                                                            | 58       |

| 4.1        | Simulated system characteristics.                                                      | 74       |

| 4.2        | Overview of all benchmarks, their periodicities, the chosen                            |          |

|            | sampling parameters and their speed and accuracy                                       | 78       |

| 5.1        | Simulated system characteristics.                                                      | 97       |

| 5.2        | SimPoint parameters. Default values used for those options                             | ,,       |

| 0.2        | not specified.                                                                         | 97       |

| 5.3        | Detailed BarrierPoint information for a variety of applica-                            |          |

|            | tions an input sizes.                                                                  | 98       |

|            | 1                                                                                      | -        |

# **List of Figures**

| 2.1  | Measured per-thread CPI for a range of SPLASH-2 bench-                                |    |

|------|---------------------------------------------------------------------------------------|----|

|      | marks, when running on 16 cores.                                                      | 8  |

| 2.2  | Measured performance of SPLASH-2 on the Intel X7460 us-                               |    |

|      | ing large and small input sets.                                                       | 9  |

| 2.3  | Resulting application runtime from an increasing reschedul-                           |    |

|      | ing cost for fft, lu.ncont and raytrace, with 4 or 16                                 |    |

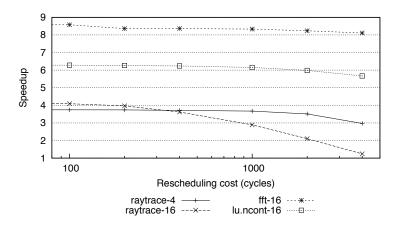

|      | threads                                                                               | 17 |

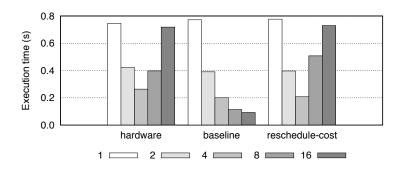

| 2.4  | Application runtime for raytrace on hardware, and sim-                                |    |

|      | ulated before and after adding basic kernel spinlock con-                             |    |

|      | tention modeling.                                                                     | 18 |

| 2.5  | Relative accuracy for the one-IPC and interval models for a                           |    |

|      | single core and 16 cores.                                                             | 21 |

| 2.6  | Absolute accuracy across all core models for a select number                          |    |

|      | of benchmarks: fft and raytrace                                                       | 22 |

| 2.7  | Application scalability for the one-IPC and interval models                           |    |

|      | when scaling the number of cores.                                                     | 22 |

| 2.8  | Detailed CPI stacks generated through interval simulation.                            | 23 |

| 2.9  | Speedup and CPI stacks for raytrace, before and after op-                             |    |

|      | timizing its locking implementation.                                                  | 24 |

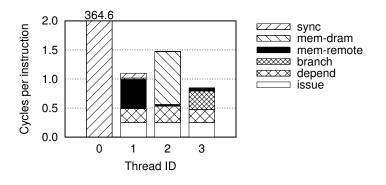

|      | $CPI \ stack \ for \ each \ of \ the \ four \ thread \ types \ spawned \ by \ dedup.$ | 25 |

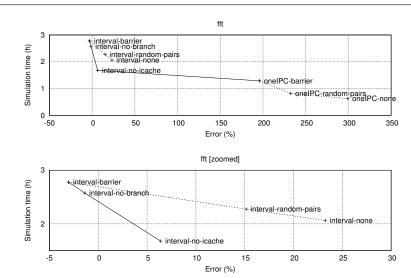

| 2.11 | Accuracy vs. speed trade-off graphs comparing both syn-                               |    |

|      | chronization mechanisms for parallel simulation                                       | 26 |

| 2.12 | Maximum absolute error by synchronization method in par-                              |    |

|      | allel simulation for simulating a 16-core system.                                     | 26 |

| 2.13 | Simulation speed of 1–16 simulated cores on an eight-core                             |    |

|      | host machine.                                                                         | 27 |

| 3.1  | Interval modeling and simulation technique taxonomy                                   | 35 |

| 3.2  | A diagram of the main components of a functionally-directed                           | 00 |

| 0.2  | simulator with 4 processor core models.                                               | 36 |

| 3.3  | A comparison between the estimation of IPC with interval                              | 00 |

| 0.0  | modeling and interval simulation.                                                     | 37 |

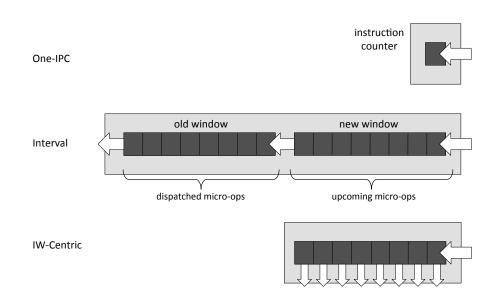

| 3.4  | A diagram of the different core performance models.                                   | 39 |

| 0.1  | r angrun of the unterent core performance models.                                     | 57 |

| 3.5        | An example of port-based issue contention in the updated interval simulation model.                                                                                                 | 43 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

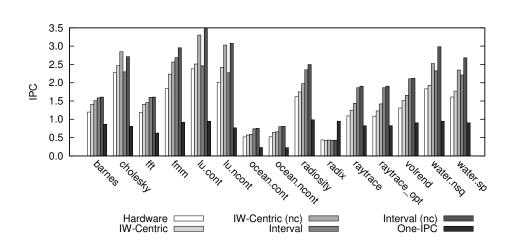

| 3.6        | Single-core IPC on real hardware and simulated using a variety of core models and benchmarks.                                                                                       | 52 |

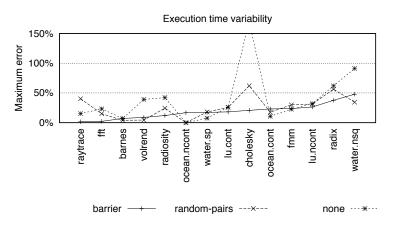

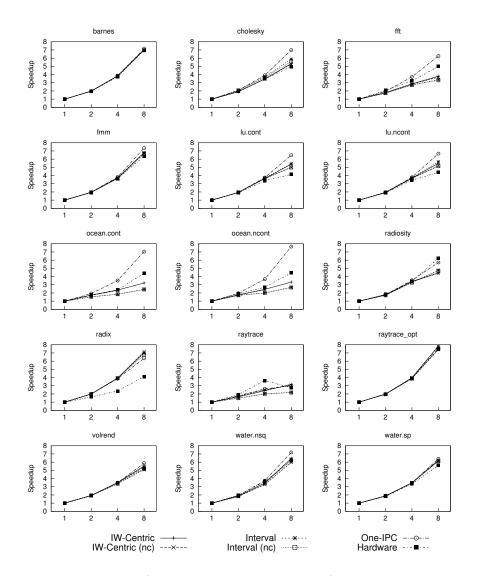

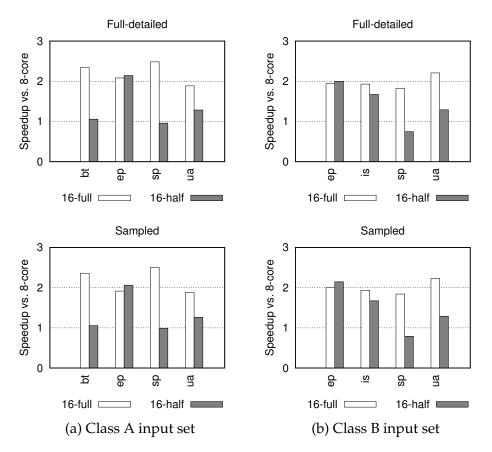

| 3.7        | Relative performance speedup predictions for the SPLASH-<br>2 applications from 1 to 8 cores.                                                                                       | 54 |

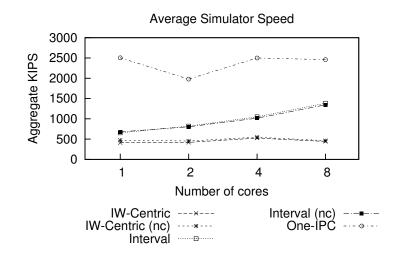

| 3.8        | Average simulator speed, in KIPS, for a variety of simulation models.                                                                                                               | 56 |

| 3.9        | Simulation speed versus modeling error of all core models for single-core runs.                                                                                                     | 57 |

| 3.10       | A comparison of L2 miss rates and application runtime of shared versus private caches, as predicted by the one-IPC, interval and instruction-window centric core models             | 59 |

| 4.1        | Proposed mechanism of fast-forwarding during multi-threaded sampled simulation.                                                                                                     | 64 |

| 4.2        | Accuracy of sampled IPC and estimated runtime for simula-<br>tions using different fast-forwarding mechanisms                                                                       | 65 |

| 4.3        | IPC trace of $N-ft$ with several visible application periodicities.                                                                                                                 | 67 |

| 4.4        | Sampling with intervals of exactly one period yields a correct IPC average; when application period and detailed length                                                             |    |

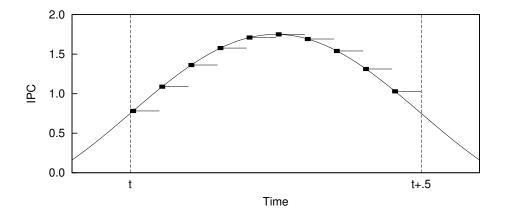

| 4.5        | do not match, sampling errors occur                                                                                                                                                 | 68 |

|            | forwarding IPC accurately tracks actual IPC.                                                                                                                                        | 68 |

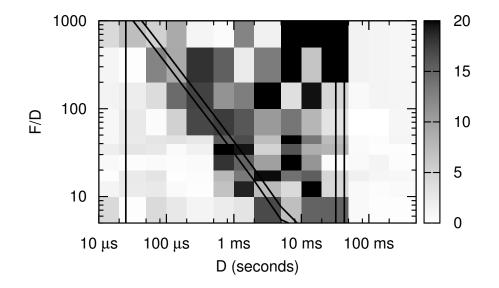

| 4.6        | BBV autocorrelation for N-ft                                                                                                                                                        | 70 |

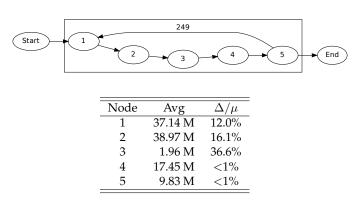

| 4.7        | Loop structure and node instruction counts for the N-lu application.                                                                                                                | 72 |

| 4.8<br>4.9 | Sampling error versus application periodicity for N-bt<br>Simulation speedup versus accuracy for all valid sampling                                                                 | 73 |

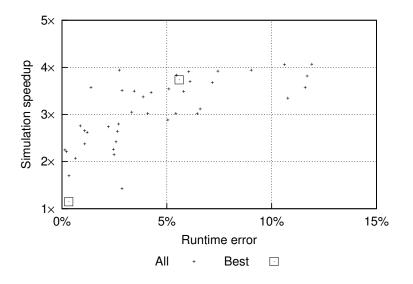

|            | parameters for O-aspi.                                                                                                                                                              | 77 |

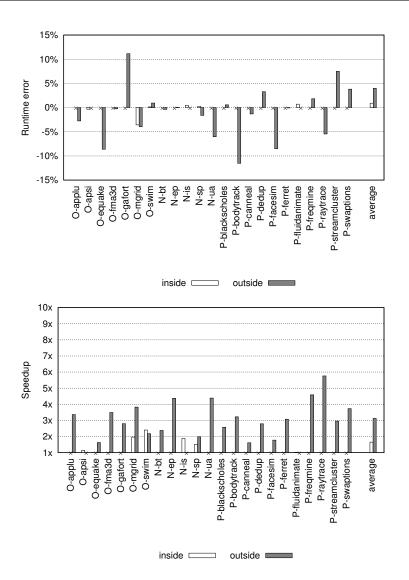

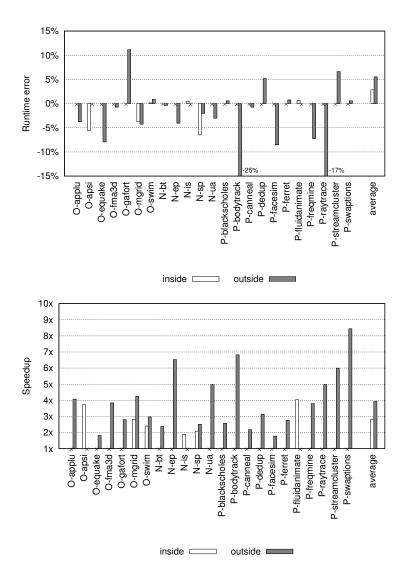

| 4.10       | Overview of sampling accuracy and speedup using the <i>pre-</i><br><i>dicted most-accurate</i> parameter set, for both <i>inside</i> and <i>outside</i><br>sampling when available. | 79 |

| 4.11       | Overview of sampling accuracy and speedup using the <i>pre-</i><br><i>dicted fastest</i> parameter set, for both <i>inside</i> and <i>outside</i> sam-                              |    |

| 4.12       | pling when available                                                                                                                                                                | 80 |

| 1 1 0      | detailed interval within each D+F region.                                                                                                                                           | 81 |

| 4.13       | Results of the architectural exploration study with speedup over the baseline architecture for all benchmarks                                                                       | 83 |

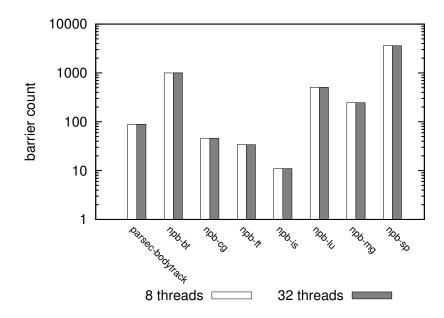

| 5.1        | Total number of dynamically executed barriers.                                                                                                                                      | 90 |

#### LIST OF FIGURES

| 5.2 | The BarrierPoint methodology flow diagram.                  | 92  |

|-----|-------------------------------------------------------------|-----|

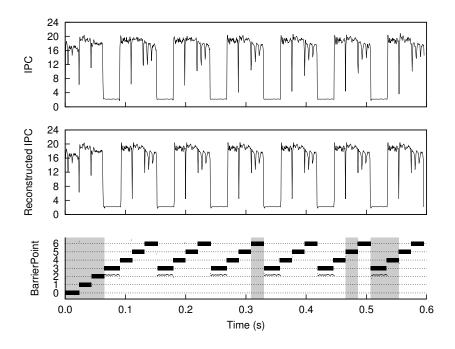

| 5.3 | Aggregate application IPC, reconstructed IPC and the se-    |     |

|     | lected barrierpoints for npb-ft                             | 96  |

| 5.4 | Percent absolute error for predicting application execution |     |

|     | time and absolute DRAM APKI difference, assuming perfect    |     |

|     | warmup                                                      | 99  |

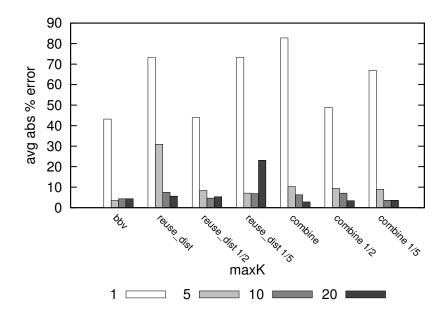

| 5.5 | Average absolute error for application execution time pre-  |     |

|     | diction for different maxK and clustering methods           | 100 |

| 5.6 | Barrierpoint selection cross-validation.                    | 101 |

| 5.7 | Percent absolute error for predicting application execution |     |

|     | time and absolute DRAM APKI difference, assuming unique     |     |

|     | warmup                                                      | 102 |

| 5.8 | Relative scaling results.                                   | 103 |

| 5.9 | Achieved speedups for each benchmark with the Barrier-      |     |

|     | Point methodology.                                          | 104 |

|     |                                                             |     |

## **List of Abbreviations**

| API    | Application Programming Interface                        |

|--------|----------------------------------------------------------|

| APKI   | Accesses per One Thousand Instructions                   |

| BBV    | Basic Block Vector                                       |

| CMP    | Chip Multi-Processor                                     |

| CPI    | Cycles per Instruction                                   |

| CPU    | Central Processing Unit                                  |

| DRAM   | Dynamic Random Access Memory                             |

| FPGA   | Field-Programmable Gate Array                            |

| GCC    | GNU Compiler Collection (formerly the GNU C Compiler)    |

| GHz    | Gigahertz (Processor Frequency)                          |

| GNU    | GNU is not Unix                                          |

| HPC    | High-Performance Computing                               |

| ILP    | Instruction-Level Parallelism                            |

| IOCOOM | In-Order Core, Out-of-Order Memory (Graphite Core Model) |

| IPC    | Instructions per Cycle                                   |

| ISA    | Instruction Set Architecture                             |

| kB     | Kilobytes (1024 bytes)                                   |

| KIPS   | One Thousand Instructions per Second                     |

| LDV    | LRU stack Distance Vector                                |

| L1     | Level 1 (Cache)                                          |

| L2     | Level 2 (Cache)                                          |

| L3     | Level 3 (Cache)                                          |

| LLC    | Last Level Cache                                         |

| MB     | Megabyte (1024 kB)                                       |

| MHS    | Memory Hierarchy State                                   |

| MIC    | Many Integrated Cores                                    |

| MIPS   | Million Instructions per Second                          |

| MLP    | Memory-Level Parallelism                                 |

| MPKI   | Misses per One Thousand Instructions                     |

| MRRL   | Memory Reference Reuse Latency                           |

| MSI    | (Modified, Shared, Invalid) Cache Coherency Protocol     |

| MTR    | Memory Timestamp Record                                  |

| NAS    | NASA Advanced Supercomputing                             |

|        |                                                          |

| NASA<br>NPB<br>NSL<br>OMP<br>OS<br>QPI<br>ROB<br>SIMD<br>SMARTS<br>SMP<br>SMT<br>SSE<br>SSE2<br>SSE2<br>SSE3<br>SSSE3<br>SV<br>TI B | National Aeronautics and Space Administration<br>NAS Parallel Benchmarks<br>No-State-Loss<br>OpenMP, Open Multi-Processing<br>Operating System<br>Quick-Path Interconnect<br>Reorder Buffer<br>Single Instruction, Multiple Data (Instruction Type)<br>Sampling Microarchitecture Simulation<br>Symmetric Multi-Processing<br>Symmetric Multi-Processing<br>Symmetric Multi-Threading<br>Streaming SIMD Extensions<br>Streaming SIMD Extensions 2<br>Streaming SIMD Extensions 3<br>Supplemental Streaming SIMD Extensions 3<br>Signature Vector<br>Translation Lookasida Buffer |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TLB                                                                                                                                 | Translation Lookaside Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\mu PC$                                                                                                                            | Micro-ops per Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### **Chapter 1**

## Introduction

#### 1.1 Context

Designs of the first digital electronics components were easy to understand and reason about. These designs could be drawn on paper, and evaluated through manual inspection or by building a system prototype. But, as designs became increasingly complicated, building the next generation of digital computers became much more difficult to do without automated verification. Additionally, as the costs to manufacture these complex machines increased, so did the requirement to produce a machine that performed as expected.

In order to meet these increasing demands, the investigation into simulation of designs before manufacturing took hold. Today, all microprocessors are simulated prior to manufacturing to validate many of their characteristics, such as performance, power and energy consumption, as well as reliability.

The primary concern of microarchitects today is the evaluation of potential performance characteristics of a new microarchitectural feature or enhancement. In this work, we provide a number of solutions for microarchitects who evaluate software on simulated hardware involving modern microarchitecture enhancements. These solutions provide faster, yet still accurate, ways to evaluate representative workloads with reduced system simulation resources.

#### 1.2 Challenges

We observe two major trends in contemporary high-performance processors as a result of the continuous progress in chip technology through Moore's Law. First, processor manufacturers integrate multiple processor cores on a single chip — multi-core processors. Twelve to sixteen cores per chip are commercially available today (in, for example, Intel's E7-8800 v2 Series, IBM's POWER8 and AMD's Opteron 6300 Series). In addition, specialized processors, such as Intel's Xeon Phi tailored for high-performance computing (HPC) applications, have more than 60 cores, while Tilera's TILE-Gx72 processor, targeted to networking applications, has up to 72. Second, we observe increasingly larger on-chip caches. Multi-megabyte caches are becoming commonplace, exemplified by the 37.5 MB L3 cache in Intel's Xeon E7-8890 v2.

These trends pose significant challenges for the tools in the computer architect's toolbox. Current practice employs detailed cycle-accurate simulation throughout the entire design cycle. While this has been (and still is) a successful approach for designing individual processor cores as well as multi-core processors with a limited number of cores, cycle-accurate simulation is not a scalable approach for simulating large-scale multi-cores with tens or hundreds of cores, for two key reasons. First, current cycle-accurate simulation infrastructures are typically single-threaded. Given that clock frequency and single-core performance are plateauing while the number of cores increases, the (simulation) gap between the performance of the target system being simulated versus simulation speed is rapidly increasing. Second, the increasingly larger caches observed in today's processors imply that increasingly larger units of work need to be simulated in order to stress the target system in a meaningful way. Finally, overall processor complexity has continued to increase as well, with the memory-hierarchy becoming a dominant factor in the simulation time of these large many-core processors.

#### **1.3 Future Simulation Requirements**

These observations impose at least three requirements for architectural simulation in the multi-core and many-core era. First, the simulation infrastructure needs to be parallel: the simulator itself needs to be a parallel application so that it can take advantage of the increasing core counts observed in current and future processor chips. A key problem in parallel simulation is to accurately model timing at high speed [56]. Advancing all the simulated cores in lock-step yields high accuracy; however, it also limits simulation speed. Relaxing timing synchronization among the simulated cores improves simulation speed at the cost of introducing modeling inaccuracies. Second, we need to raise the level of abstraction in architectural simulation. Detailed cycle-accurate simulation is too slow for multi-core systems with large core counts and large caches. Moreover, many practical design studies and research questions do not need cycle accuracy because these studies deal with system-level design issues for which cycle accuracy only gets in the way (i.e., cycle accuracy adds too much detail and is too slow, especially during the early stages of the design cycle). These first two requirements result in a direct simulation speedup allowing for higher turn-around times for early design-space exploration. After this design-space exploration has refined our target direction, a more comprehensive and detailed evaluation of the solution is needed. Therefore, the third, parallel requirement is to reduce parallel multi-threaded workloads into smaller representatives. At the late stage of an investigation, the focus changes from a latency-driven discovery phase into a throughputlimited validation where compute resources face a bottleneck. In order to improve the overall throughput in a typically resource-constrained environment (where the number of experiments to run is larger than the number of resources available), intelligent and accurate application reduction becomes critical to delivering timely results.

#### 1.4 Contributions

In this thesis, we will detail a number of solutions to tackle the requirements needed for next-generation microarchitectural simulation.

#### 1.4.1 Architectural Simulation

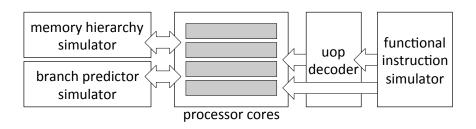

The Sniper Multi-Core Simulator brings together a number of technologies to allow for faster simulation. One of these technologies is an improved interval core model which improves performance by  $10 \times$  on average compared to detailed simulation [31]. In addition to faster core models, we integrate these models into a parallel simulator infrastructure which can lead to improved simulation performance when simulating multi-threaded targets on a multi-threaded host machine. We implemented this for the 64-bit x86 architecture and validated the models against the Intel Nehalem microarchitecture. We demonstrate how simple core models can be misleading for early design space exploration while showing how faster, more accurate simulation infrastructure can lead to predictive results for future design-space explorations.

The Sniper Multi-Core simulator was released publicly in November 2011 and has seen more than 700 downloads by researchers across the globe. Since its release, we have also presented a number of tutorials on the simulator. We presented Sniper tutorials at ISPASS 2012, ISCA 2012, HiPEAC 2013, HPCA 2013 and at IISWC 2013.

This work is published in:

T. E. Carlson, W. Heirman, and L. Eeckhout. Sniper: Exploring the level of abstraction for scalable and accurate parallel multicore simulations. In *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis* (SC), pages 52:1–52:12, November 2011

In addition to showing that sufficient detail is necessary for accurate simulation, we developed a new core model that provides a new tradeoff point for simulation speed and accuracy. This new core model, the instruction-window centric model, provides additional options for the architect to use when evaluating next-generation microarchitectural options, allowing for modeling of simple in-order, and potentially even SMT cores. Using the insights from interval simulation, these models continue to provide relatively fast simulation speeds while improving accuracy compared to hardware. In addition, we discuss an extension to the interval model, functional-unit contention, or issue contention, that provides additional accuracy with a negligible speed penalty.

This work will appear in:

T. E. Carlson, W. Heirman, S. Eyerman, I. Hur, and L. Eeckhout. An evaluation of high-level mechanistic core models. *ACM Transactions on Architecture and Code Optimization (TACO)*, 2014

#### 1.4.2 Application Sampling

Sampling of multi-threaded applications can speed up simulation of generalpurpose multi-threaded applications by reducing the amount of an application that needs to be simulated in detail. We detail a general-purpose solution of multi-threaded application sampling that allows for a reduction in the amount of work necessary to evaluate microarchitectural enhancements.

This work is published in:

T. E. Carlson, W. Heirman, and L. Eeckhout. Sampled simulation of multi-threaded applications. In *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, pages 2–12, April 2013

In addition to this work, we have also shown that for an important subset of applications, namely barrier-based multi-threaded applications, it is possible to show an even larger reduction in the amount of resources needed to accurately simulate these applications. Application barriers provide a safe point for parallelization and application comparison, where a unit of work is clearly defined. By comparing microarchitecturally independent parameters of an application, we can evaluate application similarity and select representative regions to take the place of running an entire application.

This work is published in:

T. E. Carlson, W. Heirman, K. V. Craeynest, and L. Eeckhout. BarrierPoint: Sampled simulation of multi-threaded applications. In *Proceedings of the IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS)*, pages 2–12, March 2014

#### **1.5** Structure and Overview

In this thesis, we discuss a number of solutions to improve simulation performance while maintaining high accuracy.

In Chapter 2 we discuss the Sniper Multi-Core Simulator as a faster, but still accurate alternative to cycle-level simulation.

Chapter 3 provides a new direction for processor core simulation, increasing the accuracy of high-level core models themselves with respect to hardware while maintaining high performance.

In Chapter 4 and Chapter 5 we move to an orthogonal topic compared to speeding up the simulator itself. By reducing the amount of work that needs to be done in multi-threaded applications, we can reduce the amount of an application that we need to simulate to validate our new microarchitectural ideas while still maintaining accuracy.

More specifically, Chapter 4 provides details on our sampling methodology for general purpose applications.

In Chapter 5, we discuss additional sampling methodology that provides larger application reductions for a specific class of applications, namely, barrier-based applications.

Finally, in Chapter 6, we summarize this work and describe a number of avenues for future research.

6

### **Chapter 2**

## Exploring the Level of Abstraction for Scalable and Accurate Parallel Multi-Core Simulations

This chapter presents the Sniper Multi-Core Simulator. Through the use of highlevel core and memory models and parallel simulation, Sniper is able to simulate applications at up to an aggregate of 2.0 MIPS. Sniper was validated against a real hardware platform and it maintains good accuracy across a number of benchmarks. By using Sniper and the interval simulation core models, one can more accurately model hardware platforms than compared to using One-IPC core models, while maintaining good simulation performance.

#### 2.1 Introduction

Because of the trends in computer design, namely larger core counts and cache sizes, simulation runtime has become a primary issue for determining accurate results in a relatively short timeframe. Detailed cycle-accurate simulation is too slow for multi-core systems with large core counts and large caches. Moreover, many practical design studies and research questions do not need cycle accuracy because these studies deal with system-level design issues for which cycle accuracy only gets in the way (i.e., cycle accuracy adds too much detail and is too slow, especially during the early stages of the design cycle).

This chapter deals with exactly this problem. Some of the fundamental questions we want to address are: What is a good level of abstraction for simulating future multi-core systems with large core counts and large

Exploring the Level of Abstraction for Scalable and Accurate Parallel 8 Multi-Core Simulations

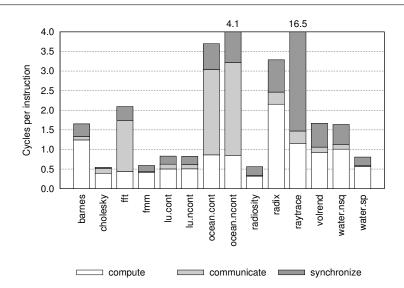

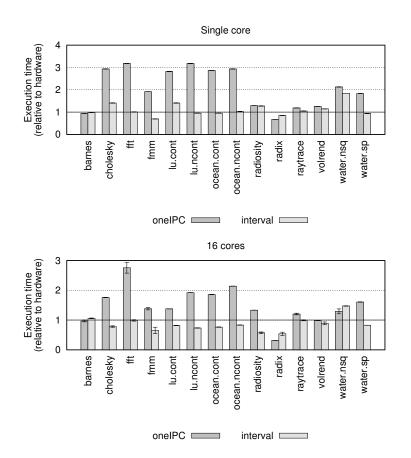

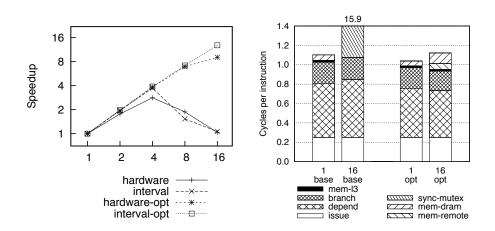

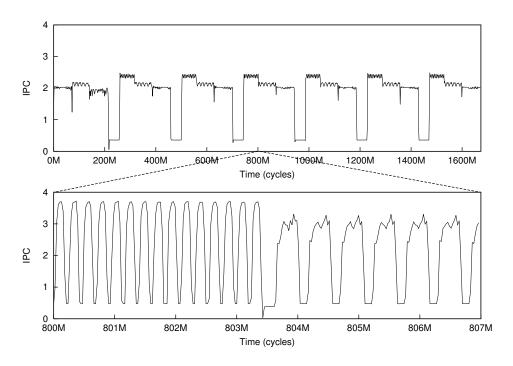

**Figure 2.1:** Measured per-thread CPI (average clock ticks per instruction) for a range of SPLASH-2 benchmarks, when running on 16 cores. (Given the homogeneity of these workloads, all threads achieve comparable performance.)

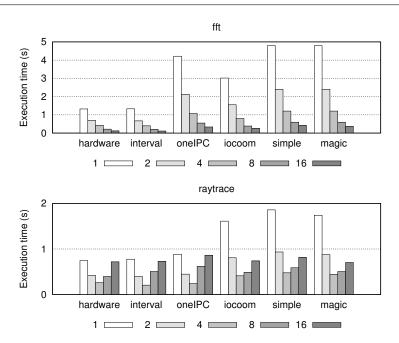

caches? Can we determine a level of abstraction that offers both good accuracy and high simulation speed? Clearly, cycle-accurate simulation yields very high accuracy, but unfortunately, it is too slow. At the other end of the spectrum lies the one-IPC model, which assumes that a core's performance equals one Instruction Per Cycle (IPC) apart from memory accesses. While both approaches are popular today, they are inadequate for many research and development projects because they are either too slow or have too little accuracy.

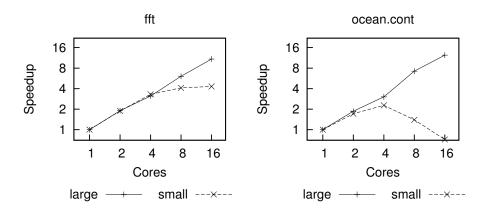

Figure 2.1 clearly illustrates that a one-IPC core model is not accurate enough. This graph shows CPI (Cycles Per Instruction) stacks that illustrate where time is spent for the SPLASH-2 benchmarks. We observe a wide diversity in the performance of these multi-threaded workloads. For example, the compute CPI component of radix is above 2 cycles per instruction, while radiosity and cholesky perform near the 0.5 CPI mark. Not taking these performance differences into account changes the timing behavior of the application and can result in widely varying accuracy. Additionally, as can be seen in Figure 2.2, simulated input sizes need to be large enough to effectively stress the memory hierarchy. Studies performed using short simulation runs (using the *small* input set) will reach different conclusions concerning the scalability of applications, and the effect on scaling of proposed hardware modifications, than studies using the more realistic *large* input sets.

The goal of this chapter is to explore the middle ground between the

**Figure 2.2:** Measured performance of SPLASH-2 on the Intel X7460 using large and small input sets.

two extremes of detailed cycle-accurate simulation versus one-IPC simulation, and to determine a good level of abstraction for simulating future multi-core systems. To this end, we consider the Graphite parallel simulation infrastructure [51], and we implement and evaluate various highabstraction processor performance models, ranging from a variety of one-IPC models to interval simulation [31], which is a recently proposed highabstraction simulation approach based on mechanistic analytical modeling. In this process, we validate against real hardware using a set of scientific parallel workloads, and have named this fast and accurate simulator Sniper. We conclude that interval simulation is far more accurate than one-IPC simulation when it comes to predicting overall chip performance. For predicting relative performance differences across processor design points, we find that one-IPC simulation may be fairly accurate for specific design studies with specific workloads under specific conditions. In particular, we find that one-IPC simulation may be accurate for understanding scaling behavior for homogeneous multi-cores running homogeneous workloads. The reason is that all the threads execute the same code and make equal progress, hence, one-IPC simulation accurately models the relative progress among the threads, and more accurate performance models may not be needed. However, for some homogeneous workloads, we find that one-IPC simulation is too simplistic and does not yield accurate performance scaling estimates. Further, for simulating heterogeneous multi-core systems and/or heterogeneous workloads, one-IPC simulation falls short because it does not capture relative performance differences among the threads and cores.

More specifically, this chapter makes the following contributions:

1. We evaluate various high-abstraction simulation approaches for

multi-core systems in terms of accuracy and speed. We debunk the prevalent one-IPC core simulation model and we demonstrate that interval simulation is more than twice as accurate as one-IPC modeling, while incurring a limited simulation slowdown. We provide several case studies illustrating the limitations of the one-IPC model.

- 2. In the process of doing so, we validate this parallel and scalable multicore simulator, named Sniper, against real hardware. Interval simulation, our most advanced high-abstraction simulation approach, is within 25% accuracy compared to hardware, while running at a simulation speed of 2.0 MIPS when simulating a 16-core system on an 8-core SMP machine.

- 3. We determine when to use which abstraction model, and we explore their relative speed and accuracy in a number of case studies. We find that the added accuracy of the interval model, more than twice as much, provides a very good trade-off between accuracy and simulation performance. Although we found the one-IPC model to be accurate enough for some performance scalability studies, this is not generally true; hence, caution is needed when using one-IPC modeling as it may lead to misleading or incorrect design decisions.

This chapter is organized as follows. We first review high-abstraction processor core performance models and parallel simulation methodologies, presenting their advantages and limitations. Next, we detail the simulator improvements that were critical to increasing the accuracy of multi-core simulation. Our experimental setup is specified next, followed by a description of the results we were able to obtain, an overview of related work and finally the conclusions.

# 2.2 Processor Core Modeling

As indicated in the introduction, raising the level of abstraction is crucial for architectural simulation to be scalable enough to be able to model multicore architectures with a large number of processor cores. The key question that arises though is: What is the right level of abstraction for simulating large multi-core systems? And when are these high-abstraction models appropriate to use?

This section discusses higher abstraction processor core models, namely, the one-IPC model (and a number of variants on the one-IPC model) as well as interval simulation, that are more appropriate for simulating multi-core systems with large core counts.

### 2.2.1 One-IPC model

A widely used and simple-to-implement level of abstraction is the so-called 'one-IPC' model. Many research studies assume a one-IPC model when studying for example memory hierarchy optimizations, the interconnection network and cache coherency protocols in large-scale multi-processor and multi-core systems [33; 52; 40]. We make the following assumptions and define a one-IPC model, which we believe is the most sensible definition within the confines of its simplicity. Note that due to the limited description of the one-IPC models in the cited research papers, it is not always clear what exact definition was used, and whether it contains the same optimizations we included in our definition.

The one-IPC model, as it is defined in this chapter, assumes in-order single-issue at a rate of one instruction per cycle, hence the name one-IPC or 'one instruction per cycle'. The one-IPC model does not simulate the branch predictor, i.e., branch prediction is assumed to be perfect. However, it simulates the cache hierarchy, including multiple levels of caches. We assume that the processor being modeled can hide L1 data cache hit latencies, i.e., an L1 data cache hit due to a load or a store does not incur any penalty and is modeled to have an execution latency of one cycle. All other cache misses do incur a penalty. In particular, an L1 instruction cache miss incurs a penalty equal to the L2 cache data access latency; an L2 cache miss incurs a penalty equal to the L3 cache data access latency, or main memory access time in the absence of an L3 cache.

### 2.2.2 One-IPC models in Graphite

Graphite [51], which forms the basis of the simulator used in this work and which we describe in more detail later, offers three CPU performance models that could be classified as one-IPC models. We will evaluate these one-IPC model variants in the evaluation section of this chapter.

The 'magic' model assumes that all instructions take one cycle to execute (i.e., unit cycle execution latency). Further, it is assumed that L1 data cache accesses cannot be hidden by superscalar out-of-order execution, so they incur the L1 data access cost (which is 3 cycles in this study). L1 misses incur a penalty equal to the L2 cache access time, i.e., L2 data cache misses are assumed not to be hidden. This CPU timing model simulates the branch predictor and assumes a fixed 15-cycle penalty on each mispredicted branch.

The 'simple' model is the same as 'magic' except that it assumes a nonunit instruction execution latency, i.e., some instructions such as multiply, divide, and floating-point operations incur a longer (non-unit) execution latency. Similar to 'magic', it assumes all cache access latencies and a fixed branch misprediction penalty.

Finally, the 'iocoom' model stands for 'in-order core, out-of-order memory', and extends upon the 'simple' model by assuming that the timing model does not stall on loads or stores. More specifically, the timing model does not stall on stores, but it waits for loads to complete (stall-on-use). Additionally, register dependencies are tracked and instruction issue is assumed to take place when all of the instruction's dependencies have been satisfied.

## 2.2.3 Sniper: Interval simulation

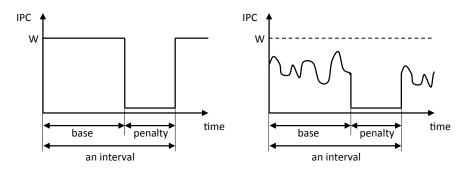

Interval simulation is a recently proposed simulation approach for simulating multi-core and multiprocessor systems at a higher level of abstraction compared to current practice of detailed cycle-accurate simulation [31]. Interval simulation leverages a mechanistic analytical model to abstract core performance by driving the timing simulation of an individual core without the detailed tracking of individual instructions through the core's pipeline stages. The foundation of the model is that miss events (branch mispredictions, cache and TLB misses) divide the smooth streaming of instructions through the pipeline into so called intervals [25]. Branch predictor, memory hierarchy, cache coherence and interconnection network simulators determine the miss events; the analytical model derives the timing for each interval. The cooperation between the mechanistic analytical model and the miss event simulators enables the modeling of the tight performance entanglement between co-executing threads on multi-core processors.

The multi-core interval simulator models the timing for the individual cores. The simulator maintains a 'window' of instructions for each simulated core. This window of instructions corresponds to the reorder buffer of a superscalar out-of-order processor, and is used to determine miss events that are overlapped by long-latency load misses. The functional simulator feeds instructions into this window at the window tail. Core-level progress (i.e., timing simulation) is derived by considering the instruction at the window head. In case of an I-cache miss, the core simulated time is increased by the miss latency. In case of a branch misprediction, the branch resolution time plus the front-end pipeline depth is added to the core simulated time, i.e., this is to model the penalty for executing the chain of dependent instructions leading to the mispredicted branch plus the number of cycles needed to refill the front-end pipeline. In case of a long-latency load (i.e., a last-level cache miss or cache coherence miss), we add the miss latency to the core simulated time, and we scan the window for independent miss events (cache misses and branch mispredictions) that are overlapped by the long-latency load - second-order effects. For a serializing instruction, we add the window drain time to the simulated core time. If none of the above cases applies, we dispatch instructions at the effective dispatch rate, which takes into account inter-instruction dependencies as well as their execution latencies. We refer to [31] for a more elaborate description of the interval simulation paradigm.

We added interval simulation into Graphite and named our version, with the interval model implementation, Sniper<sup>1</sup>, a fast and accurate multicore simulator.

## 2.2.4 Interval simulation versus one-IPC

There are a number of key differences between interval simulation and one-IPC modeling.

- Interval simulation models superscalar out-of-order execution, whereas one-IPC modeling assumes in-order issue, scalar instruction execution. More specifically, this implies that interval simulation models how non-unit instruction execution latencies due to long-latency instructions such as multiplies, divides and floating-point operations as well as L1 data cache misses, are (partially) hidden by out-of-order execution.

- Interval simulation includes the notion of instruction-level parallelism (ILP) in a program, i.e., it models inter-instruction dependencies and how chains of dependent instructions affect performance. This is reflected in the effective dispatch rate in the absence of miss events, and the branch resolution time, or the number of cycles it takes to execute a chain of dependent instructions leading to the mispredicted branch.

- Interval simulation models overlap effects due to memory accesses, which a one-IPC model does not. In particular, interval simulation models overlapping long-latency load misses, i.e., it models memorylevel parallelism (MLP), or independent long-latency load misses going off to memory simultaneously, thereby hiding memory access time.

- Interval simulation also models other second-order effects, or miss events hidden under other miss events. For example, a branch misprediction that is independent of a prior long-latency load miss is completely hidden. A one-IPC model serializes miss events and therefore overestimates their performance impact.

<sup>&</sup>lt;sup>1</sup>The simulator is named after a type of bird called a snipe. This bird moves quickly and hunts accurately.

Because interval simulation adds a number of complexities compared to one-IPC modeling, it is slightly more complex to implement, hence, development time takes longer. However, we found the added complexity to be limited: the interval model contains only about 1000 lines of code.