# An Equivalent Circuit Model of the Traveling Wave Electrode for Carrier-depletion-based Silicon Optical Modulators

Hui Yu, Wim Bogaerts, Member, IEEE

Abstract—We propose an equivalent circuit model for the coplanar waveguide (CPW) which serves as the traveling wave electrode to drive carrier-depletion-based silicon modulators. Conformal mapping and partial capacitance techniques are employed to calculate each element of the circuit. The validity of the model is confirmed by the comparison with both finite-element simulation and experimental result. With the model we calculate the modulation bandwidth for different CPW dimensions and termination impedances. A 3 dB modulation bandwidth of 15 GHz is demonstrated with a traveling wave electrode of 3 mm. The calculation indicates that by utilizing a traveling wave electrode of 2 mm we can obtain a 3 dB modulation bandwidth of 28 GHz.

*Index Terms*—Equivalent circuits, microwave propagation, optical modulation, p-n junctions, transmission lines.

## I. INTRODUCTION

Tilicon optical modulators have clearly gone through a period of rapid progress during the past several years [1], as waveguide-based silicon modulators are successfully demonstrated with different modulation mechanisms, such as: the Franz-Keldysh effect of SiGe [2], [3], the plasma dispersion effect of silicon itself [1], the electro-optical (EO) effect of strained silicon [4] and polymer-clad silicon slots [5], [6], the carrier depletion effect of the multiple quantum wells wafer-bonded on silicon [7], etc.. The most common method among these silicon modulation solutions is to exploit the plasma dispersion effect of silicon, since it doesn't need integrations of any other materials like germanium or polymer, and thus is intrinsically compatible with CMOS technology. To implement optical modulation by the plasma dispersion effect, the charge density inside an optical waveguide has to be manipulated by an electrical signal. This can be achieved by three techniques: carrier injection, accumulation and depletion [1]. Since the carrier-depletion-based modulator offers merits of processing simplicity and high operation speed, a lot of efforts are devoted to improve its performance [8]-[11]. A carrier-depletion-based modulator is implemented

Manuscript received Aug 3, 2011.

H. Yu and W. Bogaerts are with the Photonics Research Group, Department of Information Technology (INTEC), Ghent University-imec, and the Center for Nano- and Biophotonics (NB-photonics), Gent 9000, Belgium (e-mail: hui.yu@intec.ugent.be).

incorporating a PN junction inside the core of an optical waveguide. The optical modulation is achieved by reverse-biasing the junction and extracting the carriers. Its intrinsic response speed is limited by the time required for carriers to be swept out from and to return to the PN junction. This process only takes a few picoseconds since carriers drift at their saturation velocity under a large electrical field, so the potential bandwidth of such a device can reach 50 GHz [12]. However, the final operation speed is limited by particular driving schemes. Basically an optical modulator can be driven by a lumped electrode or a traveling wave electrode provided that a Mach-Zehnder (MZ) interferometer structure is employed. The lumped electrode is straightforward but it cannot fully exploit the advantage of high operation speed of the carrier-depletion-based modulator due to the RC time constant, so a traveling wave electrode is strongly desired [8], [9], [13], [14].

The operation speed of a modulator driven by a traveling wave electrode is determined by 3 factors: the velocity matching between the microwave and the optical carrier, the impedance matching and the microwave attenuation. A specific transmission line calculation is essential to achieve high speed modulation. This can be carried out by numerical field simulations employing the method of lines (MoL) [15], [16] or the finite-element method (FEM) [17]-[20]. Another technique to analyze the transmission line is to develop its equivalent circuit model under the quasi-TEM approximation [21]-[24]. Such an equivalent model is always preferable not only because it requires much less computing resource than the numerical simulation, but more importantly, because it gives a clear physical insight into the transmission line. The equivalent circuit model is used quite common for LiNbO3 modulators [22]. However, to develop this model carrier-depletion-based optical modulators turns out to be tricky, since a carrier-depletion-based modulator is not a regular laminated structure consisting of homogeneous dielectric layers with the electrode on top. A typical CMOS compatible carrier-depletion-based modulator has vias through the pre-metal dielectric layer (PMD); meanwhile the conductivity of its waveguide layer is not uniform due to different local doping levels in order to form the PN junction and the contact. These features make it a challenge to deduce an equivalent circuit model for carrier-depletion-based modulators, so in [14]

an approximate method is used for the RF design. The distributed parameters of an unloaded coplanar waveguide without the phase shifter is calculated at first, then the theoretical capacitance of the diode is added into the capacitance of the unloaded coplanar waveguide so as to estimate the overall effect. In other reported equivalent circuit models the distributed parameters are actually extracted from the FEM simulation [24] or the experimental data [23].

In this paper we deduce an analytical equivalent circuit model for the traveling wave electrode which drives carrier-depletion-based silicon modulators. It agrees quite well with the FEM simulation and the measurement result. Based on the model we design the traveling wave electrode and discuss the influence of different termination impedances. A 3 dB modulation bandwidth of 15 GHz is demonstrated with a 3 mm electrode.

### II. TRANSMISSION LINE EQUIVALENT CIRCUIT

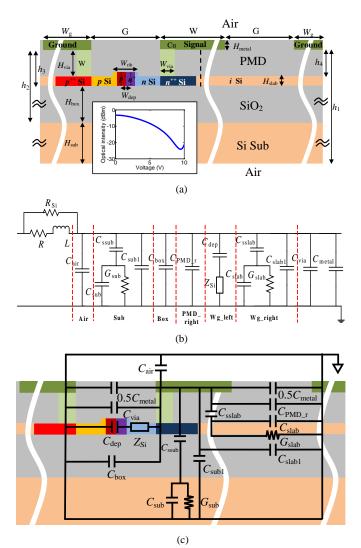

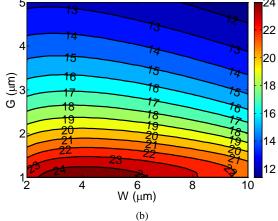

A carrier-depletion-based silicon modulator with the traveling wave electrode is a Mach-Zehnder interferometer in silicon-on-insulator (SOI). At least one of its two arms contains a PN junction so as to shift the optical phase. The cross section of a typical phase shifter is shown in Fig. 1, where a coplanar waveguide (CPW) acts as the traveling wave electrode [14], [19], [25]. Free carriers are extracted from the  $p^+$  and  $n^+$  doped regions by a reverse bias, thus a carrier depletion region is left inside the rib as outlined by the dotted line in Fig. 1(a). According to the optical waveguide theory, the modulation efficiency of this structure is proportional to the square root of the doping concentration in the carrier depletion region, so both  $p^+$  and  $n^+$  areas have a relatively high doping concentration of  $10^{18}$ /cm<sup>3</sup> [11]. The p and n type silicon in Fig. 1 is lightly doped in order to reduce the optical loss. However, a low doping concentration would lead to a high series resistance and thus limit the bandwidth. A typical value based on a trade-off between the operation speed and the optical loss can be 2× 10<sup>17</sup>/cm<sup>3</sup>. Two contact areas far away from the optical mode center are heavily doped to  $10^{20}$ /cm<sup>3</sup>. They are connected to copper electrodes by silicided regions and tungsten vias, matching a standard CMOS contacting process. Our simulation indicates that the figure of merit  $V_{\pi}L_{\pi}$  of this doping scheme is 1.92 V·cm [11]. In order to achieve enough modulation depth with a small driven signal, the phase shifter is chosen to be 2 mm. Its DC modulation characteristic is shown in the inset of Fig. 1(a). The insertion loss due to doping is 3.25 dB. Provided that the modulator is biased at 6 V where the light is sensitive to the voltage variation, a 1 V sinusoidal signal is able to extinct the beam by 5.2 dB (modulation depth of 67.7%), which is sufficient for most applications [1]. Meanwhile the width of the carrier depletion region varies within 8% of its value at the DC bias point. The traveling wave electrode in Fig. 1 is actually a nonlinear transmission line since the PN junction capacitance is voltage-dependent. However, because of the 2 mm electrode we can drive the modulator in the small signal regime. Under the small signal approximation the carrier depletion region can be

Fig. 1. (a) The cross section and the DC modulation characteristic (inset) of a typical carrier-depletion-based optical modulator in SOI with a coplanar waveguide of 2 mm as the electrode. (b) The transmission line equivalent circuit model of the traveling wave electrode shown in Fig. 1(a). (c) Relation between the circuit and the physical device.

treated as an insulator with constant width according to [26].

Relying on the specific RF frequency, silicon resistivity and device dimension, the transmission line in Fig. 1(a) supports 3 microwave propagation mechanisms which have been widely investigated: the skin effect mode, the slow wave mode and the dielectric quasi-TEM mode [27]-[29]. Here we give a brief overview about them in terms of the particular structure in Fig.1 (a):

- If the *p* and *n* regions in Fig. 1(a) which sandwich the space charge region are lightly doped, they exhibit a small dielectric loss tangent at the operation frequency. Therefore, silicon in the *p* and *n* regions acts like a dielectric. Both the transverse electric and the transverse magnetic fields can freely penetrate into the *p* and *n* doped silicon. The propagation mode is so-called "dielectric quasi-TEM mode".

- If the *p* and *n* regions are moderately doped, the dielectric relaxation frequency of the two areas can be higher than the operation frequency. This implies the free carriers outside the space charge region respond rapidly enough to shield the

interior part of the  $p^+$  and  $n^+$  doped regions from the external AC field. Therefore, the electrical field of the microwave is constrained inside the space charge region. In the meanwhile if the widths of the p and n regions are less than a skin depth, the magnetic field will penetrate through the p and n regions while the electrical field does not. Such a spatial separation between electric and magnetic energies leads to the propagation of the so-called "slow-wave mode". Its effective dielectric constant is bigger than the permittivity of any medium that comprise the transmission line [27], [28].

• If the *p* and *n* regions are heavily doped to an extremely high conductivity, their width will be bigger than the skin depth. The *p* and *n* regions behavior like two lossy conductor walls, since neither the electric nor magnetic fields can penetrate them. The mode then is called the "skin-effect mode" [27], [28].

Since the skin effect mode requires a very high doping concentration which is impractical for the optical modulator, only the slow wave and the dielectric quasi-TEM modes are relevant. Y. R. Kwon has corroborated that a quasi-TEM analysis technique is valid for the slow wave mode guided by a micron-size CPW, as the very small cross-section of the transmission line ensures that transverse fields are essentially quasi-static [30]. Above arguments manifest that a quasi-TEM analysis applies to the CPW in Fig. 1(a), so this structure can be described by an equivalent circuit effectively.

The partial-capacitance technique is employed to deduce the equivalent circuit from the structure in Fig. 1(a) [31], [32]. This method is based on the assumption that all dielectric/dielectric interfaces are along electric field lines, thus magnetic walls can be placed at these interfaces. Under this assumption a CPW on a multilayered substrate can be split into several CPWs on different single-layer substrates with modified dielectric constants. The capacitance per unit length of each partial CPW component can be calculated by conformal mapping. The capacitance of the practical CPW then is the sum of all partial capacitances. Although the partial-capacitance technique is an approximation, it is proved to be effective for the CPW on regular multilayered substrate [31]. We believe that this method also applies to the irregular structure in Fig. 1(a), since the electrical field inside the carrier depletion region is definitely parallel with the interface between the Si waveguide layer and the buried SiO<sub>2</sub> layer.

Using the conformal mapping and partial capacitance techniques, we get the equivalent circuit model shown in Fig. 1(b). We mark physical origins for all elements in Fig. 1(c). For the air space above the electrode and beneath the Si substrate, its capacitance can be written as [31], [32]

$$C_{\text{air}} = 4\varepsilon_0 \frac{K(k_0')}{K(k_0)} - 2\varepsilon_0 \frac{K(k_1')}{K(k_1)}$$

(1)

where  $K(k_i)$  is the complete elliptic integrals of the first kind. Its modulus  $k_i$  is given by

$$k_0 = \frac{x_c}{x_b} \sqrt{\frac{x_b^2 - x_a^2}{x_c^2 - x_a^2}}$$

(2)

$$k_{i} = \frac{\sinh(\frac{\pi x_{c}}{2h_{i}})}{\sinh(\frac{\pi x_{b}}{2h_{i}})} \sqrt{\frac{\sinh^{2}(\frac{\pi x_{b}}{2h_{i}}) - \sinh^{2}(\frac{\pi x_{a}}{2h_{i}})}{\sinh^{2}(\frac{\pi x_{c}}{2h_{i}}) - \sinh^{2}(\frac{\pi x_{a}}{2h_{i}})}}$$

(3)

with  $k_i' = (1 - k_i^2)^{1/2}$ ,  $x_a = W/2$ ,  $x_b = x_a + G$ ,  $x_c = x_b + W_g$  and i = 1,2,3,4. The structural parameters W, G,  $W_g$ , and  $h_i$  are denoted in Fig. 1(a). Analogically the capacitance of the buried SiO<sub>2</sub> (BOX) layer is

$$C_{\text{box}} = 2\varepsilon_0 \varepsilon_{\text{SiO}_2} \frac{K(k_2')}{K(k_2)} - 2\varepsilon_0 \varepsilon_{\text{SiO}_2} \frac{K(k_3')}{K(k_3)}$$

(4)

Unlike the BOX layer, the Silicon substrate is a semiconducting layer with non-zero conductivity, thus 4 elements are required to describe its behavior as shown in Fig. 1(b) [33]. According to [33] and [34], the transverse conductive and displacement currents in the Si substrate are represented by a conductor  $G_{\text{sub}}$  and a capacitor  $C_{\text{sub}}$  respectively

$$C_{\text{sub}} = 2\varepsilon_0 \varepsilon_{\text{Si}} \frac{K(k_1')}{K(k_1)} - 2\varepsilon_0 \varepsilon_{\text{Si}} \frac{K(k_2')}{K(k_2)}$$

(5)

$$G_{\text{sub}} = \frac{2}{\rho_{\text{sub}}} \left[ \frac{K(k_1')}{K(k_1)} - \frac{K(k_2')}{K(k_2)} \right]$$

(6)

where  $\rho_{\rm sub}$  is the resistivity of the silicon substrate. The capacitor  $C_{\rm ssub}$  which is connected in series to  $G_{\rm sub}$  and  $C_{\rm sub}$  represents the capacitance between the signal metal and the Si substrate. It can be written as

$$C_{\text{ssub}} = \varepsilon_0 \varepsilon_{\text{SiO}_2} \frac{W}{h_2} \tag{7}$$

Here we neglect the Si waveguide layer since it is very thin (0.22 um), and assume the medium for the PMD layer is also  $SiO_2$ . The capacitor  $C_{sub1}$  does not represent any substantial part in Fig. 1(a). However, it is indispensable to make the model stand up at the high frequency limit [33]. If the frequency is high enough, the conductive current is negligible compared with the displacement current, i.e. the capacitor  $C_{sub}$  effectively shunts the conductor  $G_{sub}$ . Therefore, the Si substrate can be regarded as a dielectric. According to the partial-capacitance technique, this dielectric layer should be described by the single capacitor  $C_{sub}$  in (5), so a parallel capacitor  $C_{sub1}$  is added to make sure that the total capacitance converges at  $C_{sub}$  at the high speed limit [33]

$$C_{\text{sub}} = \frac{C_{\text{sub}}C_{\text{ssub}}}{C_{\text{sub}} + C_{\text{ssub}}} + C_{\text{sub1}}$$

(8)

The capacitance  $C_{\text{sub1}}$  then is determined by (8).

The Si waveguide and PMD layers are calculated by first dividing each layer into two parts along the midline of the signal metal which is shown in Fig. 1(a) by the dash line [35]. The right side can be regarded as one half of a regular CPW, so the PMD layer can be represented by a capacitor  $(C_{\rm PMD_r})$  while the Si waveguide layer (the Si slab after waveguide etching) is described by 3 capacitors and 1 conductor  $(C_{\rm slab}, G_{\rm slab} C_{\rm sslab})$  and  $C_{\rm slab}$  1). The procedure to calculate these elements is the same as that to calculation  $C_{\rm sub}$ ,  $C_{\rm sub}$ ,  $C_{\rm sub}$ ,  $C_{\rm sub}$ , and  $C_{\rm box}$ , except that

corresponding expressions should be divided by a factor of two. On the other hand, in order to characterize the waveguide and the PMD layers on the left side, we take the impedance of the doped silicon, the capacitance of the PN junction, and the capacitance between two vias into account. Due to the small thickness of the optical waveguide, the fringe field should not be neglected when we calculate the PN junction capacitance. If the influence of rib is neglected, the doped silicon sandwiching the carrier depletion region can be regarded as two plates of finite thickness, therefore the reverse biased PN junction can be treated as a parallel-plate capacitor. W. H. Chang gave a formula to calculate the capacitance between two finite thickness plates which takes the fringing field in to account [36]. However, in his calculation the medium outside the capacitor where the fringing field exists is the same as that between the plates. In contrast the PN junction in Fig. 1(a) is between the PMD and the BOX layers, so W. H. Chang's formula should be modified

$$C_{\text{dep}} = (C_1 - \varepsilon_0 \varepsilon_{\text{Si}} \frac{H_{\text{rib}}}{W_{\text{den}}}) \frac{\varepsilon_{\text{SiO}_2}}{\varepsilon_{\text{Si}}} + \varepsilon_0 \varepsilon_{\text{Si}} \frac{H_{\text{rib}}}{W_{\text{den}}}$$

(9)

where  $H_{\text{rib}}$  and  $W_{\text{dep}}$  are the height of the rib and the width of the carrier depletion region as shown in Fig. 1(a).  $C_1$  is W. H. Chang's capacitance formula, which is not listed here for brevity. The first term in (9) represents the fringing field in the PMD and BOX layers, while the second represents the field inside the depleted Si. The impedance of the doped silicon between the contacts and the carrier depletion region is given by

$$Z_{\rm Si} = \frac{\rho_{\rm Si}}{1 + j \omega_{\rm m} \rho_{\rm Si} \varepsilon_0 \varepsilon_{\rm Si}} \left( \frac{W_{\rm rib} - W_{\rm dep}}{H_{\rm rib}} + \frac{G - W_{\rm rib}}{H_{\rm slab}} \right) \quad (10)$$

where  $\rho_{Si}$  is the resistivity of the p and n doped silicon,  $\omega_m$  is the microwave frequency. Here we assume both  $p^+$  and  $n^+$  doped regions are fully depleted. The impedance of the heavily doped silicon (the  $p^{++}$  and  $n^{++}$  regions) within the transfer length from the silicon to the silicide is neglected due to its high conductivity. The capacitance between two vias can simply be deduced from the PMD permittivity, the distance between the two vias and the via height:  $C_{\rm via} = arepsilon_0 arepsilon_{

m Si} H_{

m via} \, / \, G$  . Similarly the capacitance between side walls of the signal and the two ground electrodes is  $C_{\text{metal}} = 2\varepsilon_0 \varepsilon_{\text{Si}} H_{\text{metal}} / G$ . For simplicity we assume the medium above the CPW is air in Fig. 1(a). There may be other inter metal dielectric (IMD) layers covering the CPW in practical CMOS technology. If so, partial-capacitance technique allows us to add corresponding capacitors into the circuit so as to represent these IMD layers [31].

The last three elements to complete the equivalent circuit model are the line resistance R and the line inductance L which represent the longitudinal current flow in the electrode, and the resistance  $R_{\rm Si}$  which represents the longitudinal current in the substrate and the Si waveguide layer. At low frequency limit, the line resistance can be calculated directly by Ohm's law, while the line conductance can be derived from common magneto-static theory. Both of them are constants in this

Fig. 2. A comparion between the equivalent circuit calculation and the HFSS simulation. Values of the parameters used in the comparion are:  $W=5~\mu m$ ,  $H_{\rm metal}=0.5~\mu m$ ,  $G=2.5~\mu m$ ,  $\sigma_{\rm Si}=1/~\rho_{\rm Si}=2500~{\rm S/m}$ ,  $W_{\rm dep}=0.133~\mu m$ ,  $H_{\rm via}=1~\mu m$ ,  $W_{\rm via}=1~\mu m$ ,  $W_{\rm rib}=0.5~\mu m$ ,  $H_{\rm rib}=0.22~\mu m$ ,  $H_{\rm slab}=0.15~\mu m$ ,  $H_{\rm box}=2~\mu m$ ,  $H_{\rm sub}=500~\mu m$ , and  $\rho_{\rm sub}=0.1~\Omega \cdot m$ .

frequency range. However, as the frequency increases they become frequency dependent due to the skin-effect of the imperfect metal. In the skin-effect region, the inductance can be divided into an internal and an external part. The external inductance is frequency independent, which can be obtained from the capacitance of an air-filled CPW of the same dimension. The internal inductance can be calculated by Wheeler's incremental inductance rule [35]. The same technique is also used to calculate the line resistance in the skin-effect regime. W. Heinrich has given closed-form formulas to calculate R and L of CPWs which are accurate over a large frequency range from DC to RF [35], his result is employed in our model. Because of the interaction between the magnetic field and the Si, there is a longitudinal current inside the substrate and the Si waveguide layer. This current which parallels the current inside the metal also contributes to the loss. Y. R. Kwon points out that it can be represented by a resistance  $R_{Si}$  which is connected to R and L in parallel as shown in Fig. 1 (b) [30]. Due to the small dimension of the waveguide layer and the high resistivity substrate of the practical SOI wafer,  $R_{Si}$  is far more than the impedance given by R and L, so it can be ignored.

With the equivalent circuit in Fig. 1(b), we can get the total

shunt admittance Y and the total series impedance Z per unit length. The propagation constant  $\gamma$  and the characteristic impedance  $Z_0$  are determined by Y and Z as  $\gamma = \sqrt{ZY}$  and  $Z_{0} = \sqrt{Z/Y}$  . The effective permittivity  $\varepsilon_{\rm eff}$  and the attenuation  $\alpha$  of the transmission line are deduced from the real and the imaginary parts of  $\gamma$  respectively. To validate the equivalent circuit, we calculate  $\varepsilon_{\rm eff}$ ,  $\alpha$  and  $Z_0$ , and then compare them with the simulation result of a commercial software package HFSS which uses the FEM method to solve Maxwell's equations in RF domain. The comparison result is shown in Fig. 2. We can see the equivalent circuit agrees well with the simulation in a frequency range from 1 GHz to 55 GHz. The relative errors between calculation and simulation are equal or less than 10.9%, 4.3%, and 3.9% for  $\varepsilon_{\rm eff}$ ,  $\alpha$ , and  $|Z_0|$  respectively. The small discrepancy convinces us that the equivalent circuit model is effective for designing the traveling wave electrode. In section IV the validity of the model will be further confirmed by a comparison with the experimental measurement. At low frequency  $\varepsilon_{\rm eff}$  is higher than the permittivity of every medium in Fig. 2(a), which is a clear sign of the slow wave propagation. As the operation frequency exceeds the dielectric relaxation frequency of the p and n doped silicon, the slow wave mode evolves to the dielectric quasi-TEM mode.

### III. TRAVELING WAVE ELECTRODE DESIGN

In this section we calculate the frequency response of a carrier-depletion-based modulator with the equivalent circuit model we proposed in section 2. Supposing the voltage amplitude and the frequency of the driving signal are  $V_{\rm g}$  and  $\omega_{\rm m}$  respectively, the average voltage between the signal and the ground electrodes experienced by a photon as it travels through the phase shifter is [37]

$$V_{\text{avg}}(\omega_{\text{m}}) = \frac{V_{\text{g}}(1+\rho_{1})\exp(i\beta_{o}l)}{2[\exp(\lambda l)+\rho_{1}\rho_{2}\exp(-\lambda l)]}(V_{+}+\rho_{2}V_{-})$$

(11)

$$V_{\pm} = \exp(\pm i\phi_{\pm}) \frac{\sin\phi_{\pm}}{\phi_{\pm}}$$

(12)

$$\phi_{\pm} = \frac{(-i\gamma \mp \beta_o)l}{2} \tag{13}$$

$$\rho_1 = \frac{Z_0 - Z_s}{Z_0 + Z_s} \tag{14}$$

$$\rho_2 = \frac{Z_t - Z_0}{Z_0 + Z_t} \tag{15}$$

$$\beta_o = \frac{\omega_m}{c} n_o \tag{16}$$

where  $Z_s$  and  $Z_t$  are the impedance of the microwave source and the terminator, respectively, l is the length of the electrode, and  $n_o$  is the group refractive index of the optical mode [38], [39]. Under a small driving voltage, the modulation depth is proportional to the average RF voltage  $V_{\rm dep}$  that drops cross the carrier depletion region, which is the product of  $V_{\rm avg}(\omega_{\rm m})$  and the voltage division factor of the PN junction capacitor. By normalizing the modulation depth by its low frequency

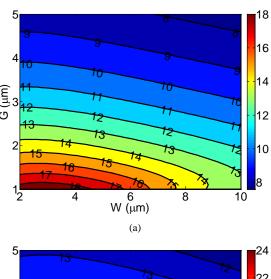

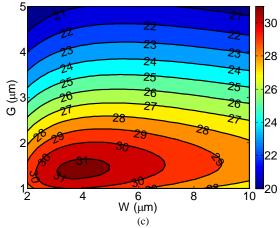

Fig. 3. 3 dB modulation bandwidth  $f_{\rm 3dB}$  vs the size of CPW for different silicon conductivities. (a)  $\sigma_{\rm si}$ =500 S/m. (b)  $\sigma_{\rm si}$ =1000 S/m. (c)  $\sigma_{\rm si}$ =2500 S/m. Parameters take the following values in the calculation:  $Z_{\rm s}$ = $Z_{\rm t}$ =50  $\Omega$ , l=2 mm,  $n_{\rm o}$ =3.59,  $H_{\rm metal}$ =0.5  $\mu$ m, and  $W_{\rm dep}$ =0.133  $\mu$ m, other parameters are the same as those in Fig. 2.

reference value, we get the frequency response of the modulator

$$m(\omega_{m}) = \frac{V_{\text{dep}}(\omega_{\text{m}})}{V_{\text{dep}}(\omega_{0})} = \frac{1}{(1 + j\omega_{0}C_{\text{dep}}Z_{\text{Si}})V_{\text{avg}}(\omega_{\text{m}})}{(1 + j\omega_{\text{m}}C_{\text{dep}}Z_{\text{Si}})V_{\text{avg}}(\omega_{0})}$$

(17)

where  $\omega_0$  is the lowest output frequency of the microwave source. It is 10 MHz in our calculation. It is necessary here to note that (17) has already taken the velocity match, impedance match, and the microwave loss into account [37]. The 3 dB

optical modulation bandwidth  $f_{3dB}$  is the frequency where  $m(\omega_m)$  falls by 50%.

Based on above discussion, we can design the CPW in terms of increasing its modulation bandwidth. As mentioned in section 2, the electrode in our bandwidth calculation is chosen to be 2 mm, while the DC bias voltage is 6 V. Of course cutting the electrode length scales up the bandwidth but with the expense of a weakened modulation depth. The width of the carrier depletion region is 133 nm according to the specific doping concentration and the bias voltage. Figure 3 presents contour maps of the 3 dB modulation bandwidth as a function of the size of CPW for different silicon conductivities  $\sigma_{si}$ . In Fig. 3(c) the modulator exhibits the largest bandwidth when the signal electrode width is between 3 µm and 6 µm. On the other hand, we can improve the modulation bandwidth by increasing the silicon conductivity  $\sigma_{si}$ , or by shrinking the gap G between the signal and the ground electrodes. This can be explained by reducing the series impedance between the carrier depletion region and the two contacts. However, the side-effect is an increased optical loss. A trade-off then depends on the particular requirement about the bandwidth and the optical loss. A typical gap G is 2.5 µm so as to isolate the optical mode from contact areas, thus from Fig. 3(c) a conductivity of  $\sigma_{si}$ = 2500 S/m is enough to support a 28 GHz bandwidth. The doping level of this conductivity is less than 1e18/cm<sup>2</sup>, so the resultant optical loss is inside the safe region.

In Fig. 3 we calculate the 3 dB modulation bandwidth which is dominated by three factors: the velocity mismatching, the impedance mismatching and the RF loss. It is necessary to single out the effect of each factor and find out which one is the major factor that limits the bandwidth. For a lossless modulator with impedance-matched load and generator ( $Z_s=Z_t=Z_0$ ), its 3 dB modulation bandwidth which is determined only by the velocity mismatching between the RF and optical signals can be calculated as [38]

$$f_{3dB} = \frac{0.18}{l(n_{\rm m} - n_{\rm o})} \text{GHz}$$

(18)

where l is the electrode length,  $n_{\rm m}$  is the microwave refractive index, and  $n_{\rm o}$  is the group refractive index of optical mode rather than the effective refractive index [39]. The microwave refractive index of the coplanar waveguide calculated in Fig. 2(a) is  $n_{\rm m} = \sqrt{\varepsilon_{\rm eff}} = 3.71$  at 28 GHz. On the other hand the group refractive index of the optical mode is  $n_{\rm o}$ =3.59 at 1.55  $\mu$ m for our waveguide. If we ignore the microwave loss and the impedance mismatching, a modulator bandwidth of 750 GHz is expected for an electrode of 2 mm according to (18). This is far beyond the final bandwidth of 28 GHz shown in Fig. 3(c). Therefore, as a result of the short electrode the bandwidth is not limited by the velocity mismatching but by the impedance mismatching together with the microwave loss.

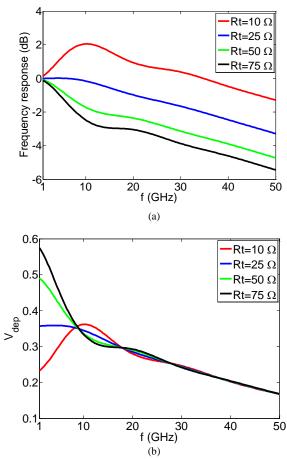

Since the output impedance of microwave sources is always 50  $\Omega$ , here we only analyze the impact of the termination impedance. The frequency responses of a MZ modulator with different terminators are displayed in Fig. 4(a). We find that a

Fig. 4. Frequency response (a) and modulation depth (b) of a modulator with different termination resistors. Parameters in the calculation are:  $W = 5 \mu m$ ,  $G = 2.5 \mu m$  and  $\sigma_{si} = 2500 \text{ S/m}$ . Other parameters are the same as those in Fig. 3.

small resistor is beneficial for increasing the bandwidth. L. Liao found the similar phenomenon in their experiment [40], he attributes the reason to the reflections resulting from the impedance mismatching which then pre-emphasizes the RF signal. Actually this phenomenon can be understood by examining the modulation depth, which can be characterized by the voltage  $V_{\text{dep}}$  as we have indicated. The evolution of  $V_{\text{dep}}$  with the frequency is presented in Fig. 4 (b), where  $V_{\text{dep}}$  is already normalized by the amplitude of the driving voltage  $V_g$ . We find that decreasing the resistance of terminator doesn't really enhance the modulation depth at high frequency. Instead, the operation bandwidth is improved by suppressing the modulation depth at low frequency [37]. At the DC limit the voltage on the transmission line is  $V_{\sigma}Z_{t}/(Z_{s}+Z_{t})$  due to the fact that the DC resistance of the CPW is negligible, so the static modulation depth degrades with reducing the termination resistance.

### IV. EXPERIMENTAL RESULT

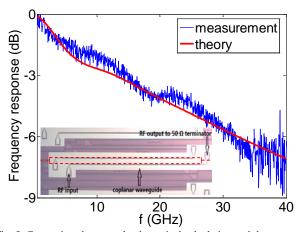

In order to fully prove its validity, we compare the equivalent circuit model with the measurement result of a practical modulator in Fig. 5. The nominal doping concentration in the  $p^+$  and the  $n^+$  doped regions is  $2 \times 10^{18}/\text{cm}^3$  for the practical device, while that in the p and the n doped regions is  $0.6 \times 10^{18}/\text{cm}^3$ . The width of the central signal metal is 6  $\mu$ m. The gap between the

Fig. 5. Comparison between the theoretical calculation and the measurement result. The inset shows a microscope image of the practical device.

central metal and two grounds is 3.5  $\mu$ m. The length of phase shifter is 3 mm. A description about the device fabrication and characterization is in [41]. The inset within Fig. 5 shows a microscope image of the device.

Since silicon in the p and the n doped regions exhibits different conductivities because of the mobility difference between electrons and holes, for simplicity we can take their mean value of  $\sigma_{\rm si}$ = 1300 S/m in the calculation. In Fig. 5 the DC reverse bias applied is -4 V. Taking the practical doping profile of gradient PN junction into account [11], we estimate the width of carrier depletion region is 0.11  $\mu$ m. Substituting these parameters into our equivalent circuit model, we calculate the frequency response with (17). In Fig. 5 there is a good agreement between the calculation and the measurement result, which confirms the validity of our model. With this device, we are able to obtain an error free modulation at 35 Gbit/s [41].

# V. CONCLUSION

In this paper we propose an equivalent circuit model for the traveling wave electrode which drives carrier-depletion-based optical modulators. Closed form expressions are deduced for every element in the circuit. Based on the model, we design the CPW for high speed modulation, and calculate the frequency response of a practical device. The calculation agrees well the final measurement result. Our calculation manifests that with a conservative doping concentration which would not cause too much optical loss and a phase shifter as long as 2 mm, a well designed CPW is able to support a 3 dB bandwidth of 28 GHz as well as a high modulation depth. This point is also confirmed by recent published results of 40 Gbit/s and 50 Gbit/s modulators which are based on similar structures [14], [42].

### REFERENCES

- G. T. Reed, G. Mashanovich, F. Y. Gardes and D. J. Thomson, "Silicon optical modulators," *Nature Photon.*, vol. 4, no. 8, pp. 518-526, Jul. 2010.

- [2] J. Liu, M. Beals, A. Pomerene, S. Bernardis, R. Sun, J. Cheng, L. C. Kimerling and J. Michel, "Waveguide-integrated, ultralow-energy GeSi electro-absorption modulators," *Nature Photon.*, vol. 2, no. 7, pp. 433-437, Jul. 2008.

[3] N. N. Feng, D. Feng, S. Liao, X. Wang, P. Dong, H. Liang, and et al, "30GHz Ge electro-absorption modulator integrated with 3μm silicon-on-insulator waveguide," Opt. Exp., vol. 19, no. 8, pp. 7062-7067, Apr. 2011.

- [4] R. S. Jacobsen, K. N. Andersen, P. I. Borel, J. F. Pedersen, L. H. Frandsen, O. Hansen, and *et al*, "strained silicon as a new electro-optic material," *Nature*, vol. 441, pp. 199-202, May. 2006.

- [5] R. Ding, T. B. Jones, Y. Liu, R. Bojko, J. Witzens, S. Huang, and *et al*, "Demonstration of a low  $V\pi L\pi$  modulator with GHz bandwidth based on electro-optic polymer-clad silicon slot waveguides," *Opt. Exp.*, vol. 18, no. 15, pp. 15618-15623, Jul. 2010.

- [6] J. H. Wülbern, S. Prorok, J. Hampe, A. Petrov, M. Eich, J. Luo, and et al, "40 GHz electro-optic modulation in hybrid silicon-organic slotted photonic crystal waveguides," Opt. Lett., vol. 35, no. 16, pp. 2753-2755, Aug. 2010.

- [7] H. W. Chen, Y. H. Kuo, J. E. Bowers, "25Gb/s hybrid silicon switch using a capacitively loaded traveling wave electrode," *Opt. exp.*, vol.18, no. 2, pp. 1070-1075, Jan. 2010.

- [8] M. R. Watts, W. A. Zortman, D. C. Trotter, R. W. Young and A. L. Lentine, "Low-voltage, compact, depletion-mode, silicon Mach-Zehnder modulator," *IEEE J. Sel. Topic Quantum Electron.*, vol. 16, no. 1, pp. 159-164, Jan-Feb. 2010.

- [9] N. Feng, S. Liao, D. Feng, P. Dong, D. Zheng, H. Liang, and *et al*, "High speed carrier-depletion modulators with 1.4V-cm VπL integrated on 0.25μm silicon-on-insulator waveguides," *Opt. Exp.*, vol. 18, no 8, pp. 7994-7999, Apr. 2010.

- [10] F. Y. Gardes, A. Brimont, P. Sanchis, G. Rasigade, D. M. Morini, L. O. Faolain, and *et al*, "High-speed modulation of a compact silicon ring resonator based on a reverse-biased pn diode," *Opt. Exp.*, vol. 17, no. 24, pp. 21986-21991, Nov. 2009.

- [11] H. Yu, W. Bogaerts, and A. D. Keersgieter, "optimization of ion implantation condition for depletion-type silicon optical modulators," *IEEE J. Quantum Electron.*, vol. 46, no. 12, pp. 1763-1768, Dec. 2010.

- [12] F. Y. Gardes, G. T. Reed, and N. G. Emerson, "A sun-micro depletion-type photonic modulator in silicon on insulator," *Opt. Exp.*, vol. 13, no. 22, pp. 8845-8854, Oct. 2005.

- [13] J. W. Park, J. B. You, I. G. Kim, and G. Kim, "High-modulation efficiency silicon Mach-Zehnder optical modulator based on carrier depletion in a PN Diode," *Opt. Exp.*, vol. 17, no. 18, pp. 15520-15524, Aug. 2009.

- [14] D. J. Thomson, F. Y. Gardes, Y. Hu, G. Mashanovich, M. Fournier, P. Grosse, and *et al*, "High contrast 40Gbit/s optical modulation in silicon," *Opt. Exp.*, vol. 19, no. 12, pp. 11507-11516, Jun. 2011.

- [15] J. Gerdes, K. H. Helf, and R. Pregla, "Full-wave analysis of traveling-wave electrodes with finite thickness for electro-optic modulators by the method of lines," *J. Lightw. Technol.*, vol. 9, no. 4, pp. 461-467, Apr. 1990.

- [16] K. Wu, C. E. Tong, and R. Vahldieck, "Microwave characteristics of high-speed traveling-wave electrooptic modulators on III-V semiconductors," *J. Lightw. Technol.*, vol. 9, no. 10, pp. 1295-1304, Oct. 1991.

- [17] S. Haxha, B. M. A. Rahman, and K. T. V. Grattan, "Bandwidth estimation for ultra-high-speed lithium niobate modulators," *Appl. Opt.*, vol. 42, no. 15, pp. 2674-2682, May. 2003.

- [18] J. C. Yi, S. H. Kim, and S. S. Choi, "Finite-element method for the impedance analysis of travling-wave modulators," *J. Lightw. Technol.*, vol. 8, no. 6, pp. 817-822, Jun. 1990.

- [19] A. Liu, L. Liao, D. Rubin, H. Nguyen, B. Ciftcioglu, Y. Chetrit, and *et al*, "High-speed optical modulation based on carrier depletion in a silicon waveguide," *Opt. Exp.*, vol. 15, no. 2, pp. 660-668, Jan. 2007.

- [20] M. Koshiba, Y. Tsuji, and M. Nishio, "Finite-element modeling of broad-band traveling-wave optical modulators," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 9, pp. 1627-1633, Sep. 1999.

- [21] H. Chung, W. S. C. Chang, and E. L. Adler, "Modeling and optimization of traveling wave LiNbO3 interferometer modulators," *IEEE J. Quantum Electron.*, vol. 27, no. 3, pp. 608-617, Mar. 1991.

- [22] S. Hopfer, Y. Shani, and D. Nir, "A novel, wideband, Lithium Niobate electrooptic modulator," *J. Lightw. Technol.*, vol. 16, no. 1, pp. 73-77, Jan. 1998.

- [23] G. L. Li, C. K. Sun, S. A. Pappert, W. X. Chen and P. K. L. Yu, "Ultrahigh-speed traveling-wave electroabsorption modulator-design and

- analysis," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 7, pp. 1177-1183, Jul. 1999.

- [24] J. Witzens, T. B. Jones and M. Hochberg, "Design of transmission line driven slot waveguide Mach-Zehnder interferometers and application to analog optical links," *Opt. Exp.*, vol. 18, no. 16, pp. 16902-16928, Aug. 2010.

- [25] D. M. Morini, L. Vivien, J. M. Fédéli, E. Cassan, P. Lyan and S. Laval, "low loss and high speed silicon optical modulator based on a lateral carrier depletion structure," *Opt. Exp.*, vol. 16, no. 1, pp. 334-339, Jan. 2008.

- [26] D. Jäger, "Slow-wave propagation along variable schottky-contact microstrip lines," *IEEE Trans. Microw. Theory Tech.*, vol. 24, no. 9, pp. 566-573, Sep. 1976.

- [27] G. W. Hughes, and R. M. White, "Microwave properties of nonlinear MIS and schottky-barrier microstrip," *IEEE Trans. Electron Devices*, vol. 22, no. 10, pp. 945-956, Oct. 1975.

- [28] H. Hasegawa, M. Furukawa, and H. Yanai, "Properties of microstrip line on Si-SiO2 system," *IEEE Trans. Microw. Theory Tech.*, vol. 19, no. 11, pp. 869-881, Nov. 1971.

- [29] J. Ko, B. Kim, and K. Lee, "Simple modeling of coplanar waveguide on thick dielectric over lossy substrate," *IEEE Trans. Electron Devices*, vol. 44, no. 5, pp. 856-861, May. 1997.

- [30] Y. R. Kwon, V. M. Hietala, and K. S. Champlin, "Quasi-TEM analysis of 'slow-wave' mode propagation on coplanar microstructure MIS transmission lines," *IEEE Trans. Electron Devices*, vol. MTT-35, no. 6, pp. 545-551, Jun. 1987.

- [31] E. Chen and S. Y. Chou, "Characteristics of coplanar transmission lines on multilayer substrates: modeling and experiments," *IEEE Trans. Microw. Theory Tech.*, vol. 45, no. 6, pp. 939-945, Jun. 1997.

- [32] E. Carlsson and S. Gevorgian, "Conformal mapping of the field and charge distributions in multilayer substrate CPW's," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 8, pp. 1544-1552, Aug. 1999.

- [33] V. Milanović, M. Ozgur, D. C. Degroot, J. A. Jargon, M. Gaitan and M. E. Zaghloul, "Characterization of broad-band transmission for coplanar waveguides on CMOS silicon substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 5, pp. 632-640, May. 1998.

- [34] D. F. Williams, M. D. Janezic, A. R. K. Ralston, and R. S. List, "Quasi-TEM model for coplanar waveguide on silicon," in *Proc. IEEE 6th Top. Meeting Electr. Perform. Electron. Packag.*, 1997, pp. 225–228.

- [35] W. Heinrich, "Quasi-TEM description of MMIC coplanar lines including conductor-loss-effects," *IEEE Trans. Microw. Theory Tech.*, vol. 41, no. 1, pp. 45-52, Jan. 1993.

- [36] W. H. Chang, "Analytical IC metal-line capacitance formulas," *IEEE Trans. Microw. Theory Tech.*, vol. 24, no. 9, pp. 608-611, Sep. 1976.

- [37] S. H. Lin, and S. Y. Wang, "High-throughput GaAs PIN electrooptic modulator with a 3-dB bandwidth of 9.6 GHz at 1.3 μm," Appl. Opt., vol. 26, no. 9, pp. 1696-1700, May. 1987.

- [38] G. Ghione, Semiconductor Devices for High-Speed Optoelectronics. New York: Cambridge University Press, 2009, ch. 6.

- [39] N. Dagli, "Wide-bandwidth lasers and modulators for RF photonics," IEEE Trans. Microw. Theory Tech., vol. 47, no. 7, pp. 1151-1171, July. 1999.

- [40] L. Liao, A. Liu, D. Rubin, J. Basak, Y. Chetrit, H. Nguyen, and et al, "40 Gbit/s silicon optical modulator for high-speed applications," *Electron. Lett.*, vol. 43, no. 22, 9944669, Oct. 2007.

- [41] H. Yu, W. Bogaerts, K. Komorowska, R. Baets, D. Korn, L. Alloatti, and et al, "Doping geometries for 40G Carrier-depletion-based silicon optical modulators," in *Proc. Optical Fiber Communication Conf. 2012*, to be published.

- [42] D. J. Thomson, F. Y. Gardes, J-M. Fedeli, S. Zlatanovic, Y. Hu, B. P. -P. Kuo, and et al, "50 Gbit/s silicon optical modulator," *IEEE Photon. Technol. Lett.*, vol. 24, no. 4, pp. 234-236, Feb. 2012.

**Hui Yu** received the Bachelor's degree in electrical engineering from Zhejiang University, Hangzhou, China, in 2003, where he also obtained his Ph.D. degree in electrical engineering in 2008.

He is currently a postdoc researcher with the Department of Information Technology, Ghent University, Gent, Belgium. His research interests include the modeling, design and fabrication of silicon active devices.

Wim Bogaerts (S'98–M'05) received the B.E. degree in applied physics from Ghent University, Ghent, Belgium, in 1998. He received the Ph.D. degree from the Department of Information Technology (INTEC), Ghent University-imec, in 2004

He is currently a professor in the Photonics Research Group at Ghent University-imec. He coordinates the activities in the field of silicon photonics process development, all-silicon

integration and photonic design tools for large-scale photonic integration.

Wim Bogaerts is a member of the IEEE Photonics Society and the Optical Society of America.