# Epitaxial Si/SiGe Multi-Stacks: From Stacked Nano-Sheet to Fork-Sheet and CFET Devices

R. Loo<sup>a,b</sup>, A. Akula<sup>a</sup>, Y. Shimura<sup>a</sup>, C. Porret<sup>a</sup>, E. Rosseel<sup>a</sup>, T. Dursap<sup>a</sup>, A. Y. Hikavyy<sup>a,\*</sup>,

M. Beggiato<sup>a</sup>, J. Bogdanowicz<sup>a</sup>, A. Merkulov<sup>a</sup>, M. Ayyad<sup>a</sup>, H. Han<sup>a</sup>, O. Richard<sup>a</sup>,

A. Impagnatiello<sup>a</sup>, D. Wang<sup>c</sup>, K. Yamamoto<sup>c</sup>, T. Sipőcz<sup>d</sup>, Á. Kerekes<sup>d</sup>, H. Mertens<sup>a</sup>,

N. Horiguchi<sup>a</sup>, and R. Langer<sup>a</sup>

<sup>a</sup> Imec, Kapeldreef 75, 3001 Leuven, Belgium

<sup>b</sup> Ghent University, Department of Solid-State Sciences, Krijgslaan 281, building S1, 9000 Ghent, Belgium

<sup>c</sup> Faculty of Engineering Sciences, Kyushu University, 6-1 Kasuga-koen, Kasuga, Fukuoka, Japan

<sup>d</sup> Semilab Semiconductor Physics Laboratory Co. Ltd., Prielle Kornélia u. 2. H-1117 Budapest, Hungary

\* Currently at Soitec, 922 Parc technologique des Fontaines, Chem. des Franques, 38190 Bernin, France

> After a short description of the evolution of metal-oxidesemiconductor (MOS) device architectures and the corresponding requirements on epitaxial growth processes, the manuscript describes the material properties of complicated Si/SiGe multi-layer stacks used for complementary field effect transistor (CFET) devices. They contain two different Ge concentrations and have been grown using conventional process gases. A relatively high growth temperature is used to obtain acceptable Si and SiGe growth rates. Still island growth has been suppressed for Ge concentrations up to 40%. Excellent structural and optical material properties of the Si/SiGe multi-layer stack will be reported, with up to 3 + 3 Si channels in the top and bottom part of the stack, respectively. The absence/presence of lattice defects has been verified by room temperature photoluminescence measurements. Photoluminescence measurements at low temperatures are used to study band-to-band luminescence from individual sub-layers and to illustrate the optical material quality of the CFET stack.

# Introduction

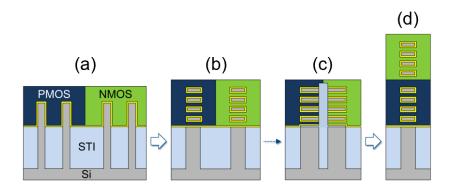

The scaling evolution from stacked nano-sheet devices to fork-sheet devices and complementary field effect transistor (CFET) architectures went together with increased complexities of the epitaxial growth schemes (Fig. 1). This is valid for both the Si/SiGe multi-layers, which define the thickness of the nano-sheet channels as well as the vertical distance between individual nano-sheets, and for the epitaxially grown source/drain (SD) layers which require a continuous increase in active doping concentration and a reduction in thermal budget without compromising material quality.

Figure 1. Evolution of MOS device architecture. a) Triple-gate finFETs are being replaced by b) gate-all-around (GAA) vertically stacked lateral nano-sheet FETs, which could potentially evolve into c) the so-called fork-sheet configuration wherein neighboring devices are separated by a dielectric wall. Beyond that, d) stacking of N/PMOS devices on top of each other in a CFET structure is currently being explored as an attractive concept for ultimate CMOS scaling.

Fork-sheet transistors are lateral nano-sheet devices with a forked gate structure (Fig. 1c) (1,2). The physical separation of n- and p-devices by a dielectric wall enables device scaling and, consequently, sheet width maximization within the limited footprint of low-track-height standard cells. Bottom dielectric isolation has been proposed to circumvent the junction isolation trade-off between punch-through suppression on the one hand and junction leakage and capacitance on the other hand (3). A typical fabrication scheme includes the challenging epitaxial growth of fully strained Si/Si<sub>1-y</sub>Ge<sub>y</sub>/multi-{Si<sub>1-x</sub>Ge<sub>x</sub>/Si} epi stacks (y>x) where the bottom Ge-rich Si<sub>1-y</sub>Ge<sub>y</sub> layer is later replaced by a SiN/SiCO isolation (4,5).

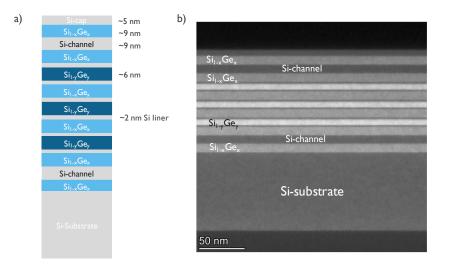

In the CFET architecture, N- and P-MOS devices are placed on top of each other, thus completely removing the area consumption by the N-P spacing. This allows for further maximizing the effective channel width and, hence, the drive current (6-12). The architecture can be fabricated following either a monolithic or a sequential approach. In the first option, N- and P-MOS transistors are built on the same wafer, while the sequential fabrication flow is based on wafer-to-wafer bonding techniques. The strengths and challenges of both approaches are discussed in (9). In the monolithic approach, device fabrication starts with the epitaxial growth of an even more complicated Si/SiGe multistack with two different Ge concentrations (Fig. 2) (9,12,13), and where Ge-rich Si<sub>1-v</sub>Ge<sub>v</sub> layers are later replaced by isolating dielectrics forming a so-called middle dielectric isolation (MDI) (9,12). Owing to the very small dimensions (e.g., sub-10 nm nano-sheet channel width), high etching selectivity of the  $Si_{1-y}Ge_y$  layers towards both  $Si_{1-x}Ge_x$  and  $Si_y$ . and excellent process controls are mandatory. This sets stringent requirements on the epitaxial layer stacks (thicknesses and composition control, sharpness of interfaces, and absence of strain relaxation) (4,5,13,14) as well as on the Si<sub>1-y</sub>Ge<sub>y</sub> etch process (high selectivity and limited consumption of  $Si_{1-x}Ge_x$  and Si (14-17).

High performance metal / SD junctions are key to alleviate scaling-related contact issues in these devices (18). Selective epitaxial growth (SEG) processes yielding heavy active doping are therefore required, in addition to introducing innovative contact materials

and designs (19-21). The resulting electrical performance is, however, restricted by doping solubility limits and loading effects (impact of substrate patterning) inherent to scaling. Those must be circumvented to enable the upcoming generations of components. Moreover, novel device architectures add stringent constraints regarding pre-epi cleaning strategies, thermal budgets, and stability. Changes in how devices are connected are also being introduced into the roadmap. To address both wiring and power delivery bottlenecks, part of the interconnects are being moved to the wafer backside (21). This backside processing starts with an extreme wafer thinning, for which a thin SiGe etch stop layer is being considered to compensate for within-wafer non-uniformities of the Si substrate removal process (22-24).

The current work describes the material requirements for the different layers used in monolithic CFET device flows and the progress made on the associated epitaxial growth. The epitaxial growth processes used to deposit Si/Si<sub>1-x</sub>Ge<sub>x</sub> multi-layers for GAA devices (Fig. 1b) is well understood and has been reported in (25,26). Previous learnings from imec about the selective epitaxial growth of extremely highly doped SD layers as well as the growth against the vertical sidewalls of the nanosheets have been reported in e.g. (19,20,27,28). More recent results will be discussed in (29,30).

Figure 2. a) Schematic cross-section and b) cross sectional HAADF STEM image of a Si/SiGe multi-stack used for CFET devices with one channel for both the p-type and the n-type devices.

## **Experimental**

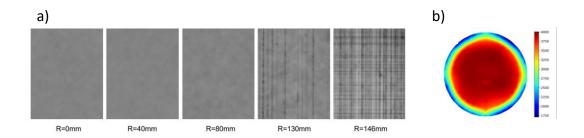

The epitaxial layers were grown in a production compatible ASM Intrepid<sup>TM</sup> RP-CVD cluster tool. Before layer deposition, the 300 mm Si(001) wafer surface received a conventional wet-chemical clean. Depending on the incoming wafer, the native oxide was either removed in-situ by a thermal treatment at a sufficiently high temperature (> 1000°C) or by a wet HF clean followed by an in-situ anneal at 800 – 900°C. Careful optimization of the temperature profile within the epi-reactor allows to avoid the formation of slip lines during the pre-epi bake and to deposit epitaxial layers with a uniform thickness over the wafer (relative standard deviation < 1.3%). Epitaxial growth was carried out at reduced

pressure using H<sub>2</sub> as carrier gas and conventional precursor gases (SiH<sub>4</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, and GeH<sub>4</sub> (5% diluted in H<sub>2</sub>)). The epitaxial layer stack consists of a complicated Si/SiGe multi-stack with two different Ge concentrations (Fig. 2). The Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-y</sub>Ge<sub>y</sub> layers with y > x are separated by thin Si layers. After fin patterning, the Si<sub>1-y</sub>Ge<sub>y</sub> layers are replaced by SiN/SiCO (9,12). The presence of the Si liners prevents vertical etching of Si<sub>1-x</sub>Ge<sub>x</sub> during Si<sub>1-y</sub>Ge<sub>y</sub> removal (14). The abruptness of the compositional change at Si/SiGe interfaces is limited by Ge segregation occurring during Si layer growth on the SiGe surface. The most abrupt interfaces have been obtained when using a chlorinated chemistry (31,32).

A broad range of material characterization techniques have been used to study the epitaxial material properties. For a review of the metrology challenges encountered for GAA structures (including CFET) the reader is referred to the references (33) and (34). The interface abruptness between two sublayers of the epi-stack has been characterized by e.g. high-angle annular dark field scanning transmission electron microscopy (HAADF-STEM) (35) and soft X-ray reflectometry (36). Room temperature photoluminescence (PL) measurements have been performed using a production compatible En-Vision-3000 system from Semilab (37,38). This inspection system allows for automatic 200/300 mm wafer tests and targets quick, non-contact and non-destructive detection of nm scale PL active buried defects. The Micro-PL measurement, for characterizing optical properties of materials on a micron scale, is based on a high intensity illumination at 532 nm. The detection is carried out at either band-to-band PL, with a peak intensity at 1100 nm (1.127 eV), or at 1400 nm long pass filter PL, 1400-1600 nm (0.89-0.78 eV). Macro-PL applies 808 nm illumination for full wafer mapping. Temperature- (9-300 K) and power-dependent PL measurements, were used to study band-to-band luminescence. A continuous wave laser beam with an excitation wavelength of 532 nm and a spot diameter of ~ 2  $\mu$ m creates excitons. Because of the valence band offsets, most excitons are trapped by the SiGe layers and the luminescence from the different layers is collected by a 50x object lens, dispersed by a Horiba LabRAMHR-PL system, and detected by an extended InGaAs array sensor cooled at 180 K.

# **Results and Discussion**

#### Structural material properties of the CFET stack

The epitaxial growth temperature has been chosen to be low enough to obtain two dimensional Si<sub>1-y</sub>Ge<sub>y</sub> growth, without three dimensional islands, for single layers as well as for the complete CFET stack with Ge concentrations up to 40% (Fig. 2b). The smooth surface of the resulting CFET stacks is confirmed by both Scanning Electron Microscope (SEM) and surface haze measurements. No larger defects are observed across the wafer surface. Except for the area near the wafer edge, misfit dislocations are avoided by choosing suitable process conditions and taking limitations in layer compositions and individual thicknesses into account. The crystalline defect density, as measured for the layers shown in Fig. 2b, lies indeed below the detection limit of Electron Channeling Contrast Imaging (ECCI), which was in the given case ~  $1 \times 10^5$  defects/cm<sup>2</sup>. Near the wafer edge, misfit dislocations are nevertheless present, because the wafer edge reduces the critical thickness for layer relaxation (26). The absence of defects in the inner part of the wafer surface and the presence of misfits near the wafer edge is confirmed by room tempe-

Figure 3. a) 1400 nm long pass filter PL measured on an epitaxial CFET stack from center to edge over the wafer. The field of view is  $140x175 \ \mu m^2$  and R is the radial distance from the wafer center. b) PL intensity map.

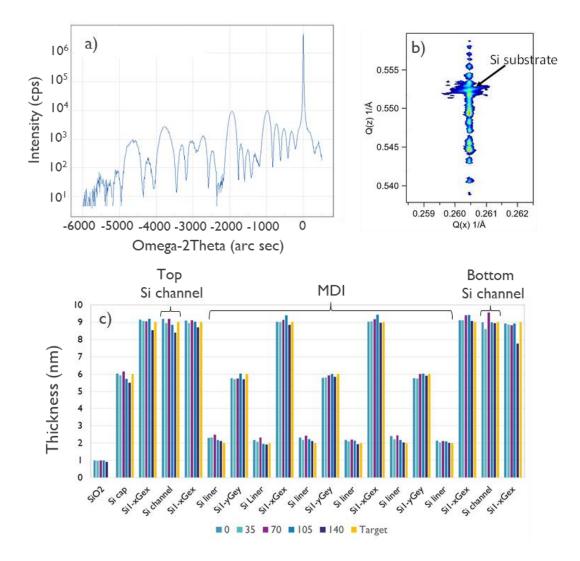

Figure 4. a) XRD  $\omega$ -2 $\theta$  scan acquired around the Si 004 Bragg reflection for the CFET stack shown in Fig. 2b, grown on top of a Si:P ground plane doped layer, b) XRD RSM acquired for the same stack around the Si 113 Bragg reflection, and c) thicknesses of the individual layers as extracted from XRR and for different positions over the wafer, where the distance from the wafer center is given in mm.

rature PL measurements and reflected in the full wafer color map of the Macro-PL intensity (Fig. 3). A reduction of the growth temperature, together with the use of higher order precursors (14,25) might enable to suppress the formation of misfit dislocations at the wafer edge. However, avoiding reactions in the gas phase needs careful attention as it results in the formation of amorphous defects on the wafer surface which, in turn, also can act as nucleation sources for misfit dislocations, despite the lower processing temperature (39). Similar layers stacks but without the presence of misfit dislocations at the wafer edge will be reported by Rengo *et al* (40).

The material quality is further confirmed by X-Ray Diffraction (XRD) (Fig. 4a), X-Ray Reflectivity (XRR), and XRD Reciprocal Space Maps (RSM) (Fig. 4b). The latter confirms the absence of strain relaxation. The peaks constituting the omega-2theta ( $\omega$ -2 $\theta$ ) diffraction spectrum reflect the high material quality. The individual peaks are well resolved, and the spectrum has a low background signal. Fig. 4c shows an example of the within wafer uniformity of individual layer thicknesses as obtained after optimization of the process settings.

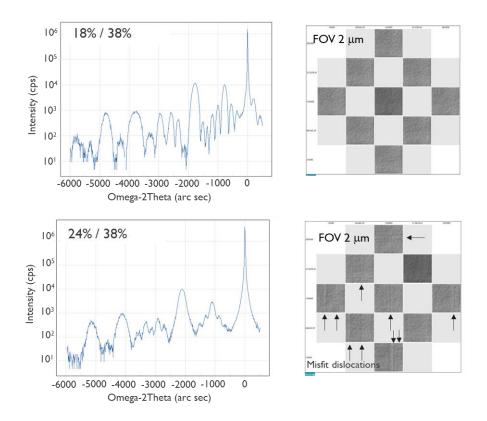

The Ge concentrations in the Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-y</sub>Ge<sub>y</sub> layers might be adapted in function of the characteristics of the selective etching routines. Keeping the individual layer thicknesses unchanged, critical Ge concentrations exist, above which layer relaxation of the Si/SiGe multi-stack cannot be avoided. As an example, Fig. 5 compares the XRD  $\omega$ -2 $\theta$ scans and plan-view (PV) SEM images of multi-stacks where the Si<sub>1-x</sub>Ge<sub>x</sub> layers contain either 18% Ge (top) or 24% Ge (bottom) while the Si<sub>1-y</sub>Ge<sub>y</sub> layers have in both cases the same nominal Ge concentration of 38%. The stack with the lower Ge concentration is fully strained and the XRD spectrum is well defined with well resolved peaks and a low background signal. The PV-SEM images show a smooth surface without suggesting the presence of misfit dislocations at the underlying Si/Si<sub>1-x</sub>Ge<sub>x</sub> and/or Si/Si<sub>1-y</sub>Ge<sub>y</sub> interfaces. For the stack with the higher Ge concentration, misfit dislocations are detected at different positions of the wafer surface. The corresponding XRD spectrum is less well defined with a higher background and the peaks are less well resolved.

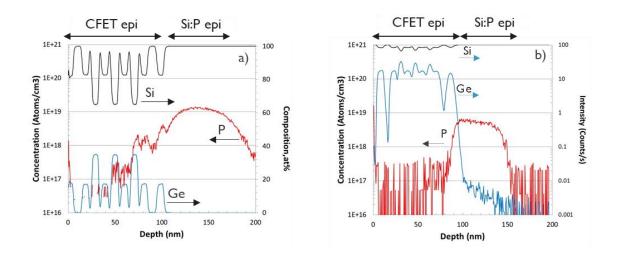

Also, the presence of a Si:P ground plane doped layer, eventually considered for bottom isolation, increases the risk for a degraded material quality, especially when the Si:P ground plane doped layer is formed by ion implantation. In addition, there is a risk for P segregation into the Si/SiGe multi-stack, which also affects final device properties. Both issues can be avoided by using an optimized combination of ex-situ wet-chemical and insitu thermal pre-epi cleaning routines, as confirmed by Extremely Low Impact Energy Secondary Ion Mass Spectrometry (EXLIE-SIMS) (41) shown in Fig. 6.

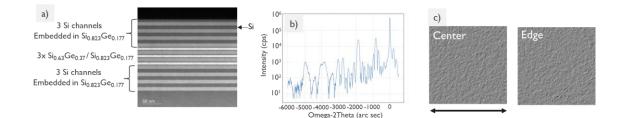

The optimized epitaxial growth of the Si/Si<sub>1-x</sub>Ge<sub>x</sub>/Si<sub>1-y</sub>Ge<sub>y</sub> multi-stack can be extended to multiple channels (Fig. 7). Again, no larger defects are observed across the wafer surface and the epitaxial layer remains free of misfit dislocations, except for the area near the wafer edge. The XRD signature is close to the predicted spectrum. The different peaks are well resolved, and the low background illustrates the high material quality. The differences between the spectrum shown in Fig. 7b with respect to the one shown in Fig. 4a, are the result of the additional layers in the stack.

Figure 5. Left: XRD  $\omega$ -2 $\theta$  scans acquired around the Si 004 Bragg reflection for CFET stacks with different Ge concentrations in the Si<sub>1-x</sub>Ge<sub>x</sub> layers and grown on top of Si:P ground plane doped layers. Right: plan view SEM inspections taken on multiple locations of the wafer surface. Si<sub>1-x</sub>Ge<sub>x</sub> layers contain 18% Ge (top) and 24% Ge (bottom). In both cases the Si<sub>1-y</sub>Ge<sub>y</sub> layers contain 38% Ge.

Figure 6. P, Si, and Ge profiles as measured by EXLIE-SIMS for epitaxial CFET stacks grown on Si:P. a) Non-optimized pre-epi treatment before growing the CFET stack and b) optimized pre-epi treatment for which the P segregation from the bottom Si:P layer into the CFET multi-stack is clearly suppressed. In b), the measurement conditions were optimal for P, but not for Si and Ge.

Figure 7. Si/SiGe multi-stack for CFET devices containing 3 + 3 channels in both the top and the bottom part. a) Cross-sectional HAADF STEM, b) XRD  $\omega$ -2 $\theta$  scans acquired around the Si 004 Bragg reflection, and c) plan view SEM inspections taken at the center and edge of the wafer.

# Interface sharpness

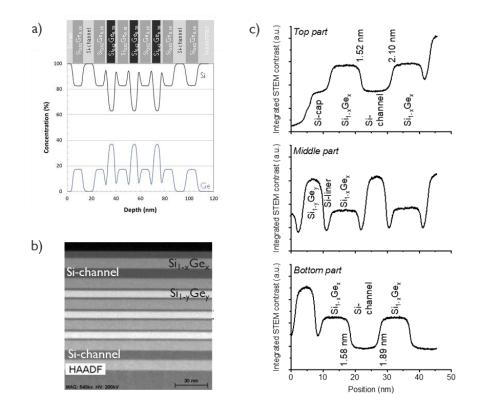

The presence of thin Si liners in between the Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-y</sub>Ge<sub>y</sub> layers aims to prevent vertical etching of Si<sub>1-x</sub>Ge<sub>x</sub> during the lateral Si<sub>1-y</sub>Ge<sub>y</sub> removal (14). Still, the required high etching selectivity of the Si<sub>1-y</sub>Ge<sub>y</sub> layers towards both Si<sub>1-x</sub>Ge<sub>x</sub> and Si, and also of Si<sub>1-x</sub>Ge<sub>x</sub> towards Si later in the processing flow, sets requirements on the sharpness of the interfaces between different layers. EXLIE-SIMS (41), Energy-Dispersive X-ray spectroscopy (EDX), integrated STEM contrast analysis (35), and soft X-ray reflectometry (36) confirm the sharp gradients in Ge concentration at the different interfaces. A typical example of Ge and Si profiles as measured by EXLIE-SIMS is shown in Fig. 8a, which also confirms the layer-to-layer reproducibility in composition. All interfaces are extremely sharp. The depth resolution of the EXLIE-SIMS is therefore not sufficient to extract interface steepness.

The interface abruptness has nevertheless been extracted from horizontally integrated HAADF-STEM contrast images (Fig. 8b). The HAADF-STEM contrast is approximately proportional to the square of the atomic number, which allows to extract the Ge depth profiles (Fig. 8c). integrated contrast has been fitted with the Sigmoid function which is expressed as:

$$f(x) = \frac{c}{1 + e^{\frac{\pm (z_0 - x)}{\tau}}} + b$$

[1]

where *C* and *b* are constants and  $z_0$  denotes the position of the interface. The value of  $4\tau$  is used as the interface thickness (42). Note that the integrated contrast profiles shown in Fig. 8c have been obtained by integrating over an area of the TEM specimen. The extracted  $4\tau$  values include contributions from interfacial roughness and are therefore larger than the values obtained when extracting the contrast profile from a vertical line scan.

The interfaces from the Si-channel (bottom side) towards  $Si_{1-x}Ge_x$  (top side) are, as expected, slightly sharper than the interfaces from  $Si_{1-x}Ge_x$  (bottom side) towards the Sichannel (top side) (Fig. 8c, top and bottom figures). For the latter one, the abruptness of the compositional change is limited by Ge segregation, occurring during Si layer growth on the Si<sub>1-x</sub>Ge<sub>x</sub> surface. The Si-liners placed in-between Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-y</sub>Ge<sub>y</sub> layers, are too thin to enable extraction of interfacial thicknesses between the Si<sub>1-y</sub>Ge<sub>y</sub> and Si layers, as Si-top and bottom interfaces are overlapping (Fig. 8c, middle part). The presence of the Si-liners does allow a successful selective  $Si_{1-y}Ge_y$  removal without damaging  $Si_{1-x}Ge_x$  as reported in (9) and (12), which illustrates the interfacial sharpness in a different way.

Figure 8. Si/SiGe multi-stack as used for CFET devices with one channel for both the ptype and the n-type devices. a) Ge and Si EXLIE-SIMS profiles, b) cross-sectional HAADF STEM, and c) horizontally integrated contrast profiles extracted from high resolution HAADF STEM images. The numbers mentioned at the Si<sub>1-x</sub>Ge<sub>x</sub>/Si and Si/ Si<sub>1-x</sub>Ge<sub>x</sub> interfaces are the interface thicknesses obtained after fitting the contrast profiles with the Sigmoid function.

## Low temperature photoluminescence

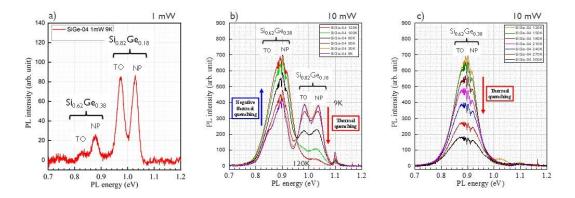

The low temperature PL spectra contain four well defined luminescence peaks (Fig. 9a). By temperature- and excitation-power-dependent measurements, combined with a comparison with the PL spectra obtained on reference samples which contain only one group of SiGe layers (either the low-Ge Si<sub>1-x</sub>Ge<sub>x</sub> or the Ge-rich Si<sub>1-y</sub>Ge<sub>y</sub>), the peaks could be assigned to the no-phonon (NP) transitions and their TO-phonon replicas arising from the Si<sub>1-x</sub>Ge<sub>x</sub> and Si<sub>1-y</sub>Ge<sub>y</sub> layers with the two different Ge concentrations (43,44). The largest fraction of the laser light is absorbed in the Si substrate where consequently the majority of the excitons are created. At the lowest measurement temperature, these excitons are trapped by the SiGe layer which is next to the substrate. This explains the higher intensity of the low-Ge Si<sub>1-x</sub>Ge<sub>x</sub> luminescence. With increasing laser intensity, the NP peaks shift to a higher energy as the luminescence changes from localized excitons (LE's) to bound excitons (BE's), and free excitons (FE's) (not shown). Increasing the measurement temperature results in a thermal quenching of the low-Ge Si<sub>1-x</sub>Ge<sub>y</sub> luminescence (Fig. 9b). Excitons can

leave the low-Ge Si<sub>1-x</sub>Ge<sub>x</sub> layer(s) and are trapped by the Ge-rich Si<sub>1-y</sub>Ge<sub>y</sub> layers which have a larger valence band offset, with respect to Si. The fact that excitons can escape from low-Ge Si<sub>1-x</sub>Ge<sub>x</sub> layer(s) and move to Ge-rich Si<sub>1-y</sub>Ge<sub>y</sub> layers without being trapped by non-radiation recombination centers illustrates the high material quality of the epitaxial stack and the absence of defects. Above ~ 120 K, there is no luminescence signal at energies above 0.9 eV (no luminescence arising from the low-Ge Si<sub>1-x</sub>Ge<sub>x</sub> layers) and the PL intensity at 0.8 – 0.9 eV shows normal thermal quenching.

Figure 9. PL intensity as function of PL energy as measured on a complete CFET stack. a) Spectrum measured at 9 K and an excitation power intensity of 1 mW. b) and c) Temperature dependent PL spectra measured at an excitation power intensity of 10 mW and in temperature regimes of 9 - 120 K and 120 - 300 K, respectively.

#### Conclusions

The material properties of Si/SiGe multi-layer stacks used for CFET devices have been presented. The epitaxial layers contain two different Ge concentrations and have been grown using conventional process gases. Despite the relative high growth temperature, island growth can be suppressed for Ge concentrations up to 40%. Excellent material properties have been reported. A carefully optimized pre-epi surface preparation routine prevents both degradation of the material quality as well as phosphorus segregation when depositing the CFET stack on top of a Si:P ground plane doped layer. The optimized epitaxial growth process allows the deposition of the Si/SiGe CFET stack with multiple channels as demonstrated for 3 + 3 channels at the top and bottom part of the layer stack. Room temperature PL measurements allow for a fast and reliable verification of the absence/presence of lattice defects including full wafer mapping. Complementary low temperature PL measurements have been used to study the optical material properties of individual sublayers and to further demonstrate the material quality of the CFET stack.

#### Acknowledgments

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007254. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Netherlands, Germany, France, Czech Republic, Austria, Spain, Belgium, Israel. The project is also supported by the Chips Joint

Undertaking and its members, including the top-up funding by VLAIO. Parts of this work were supported by a JSPS-FWO Bilateral Joint Research Project (file number: VS01522N). In addition, Roger Loo acknowledges the Flemish Research Foundation FWO for allocating a travel grant for the participation in the ECS Pacific Rim Meeting on electrochemical and solid state science 2024 (PRiME 2024), Symposium G03: SiGe, Ge & Related Compounds: Materials, Processing and Devices (file number: K1A8N24N). The imec core CMOS program members, local authorities and the imec pilot line are acknowledged for their support.

### References

- P. Weckx, J. Ryckaert, V. Putcha, A. De Keersgieter, J. Boemmels, P. Schuddinck, D. Jang, D. Yakimets, M. G. Bardon, L. -Å. Ragnarsson, P. Raghavan, R. R. Kim, A. Spessot, D. Verkest, and A. Mocuta, 2017 IEEE International Electron Device Meeting (IEDM), 20.5.1. (2017).

- H. Mertens, R. Ritzenthaler, Y. Oniki, B. Briggs, BT Chan, A. Hikavyy, T. Hopf, G. Mannaert, Z. Tao, F. Sebaai, A. Peter, K. Vandersmissen, E. Dupuy, E. Rosseel, D. Batuk, J. Geypen, G.T. Martinez Alanis, D. Abigail, E. Grieten, K. D'have, J. Mitard, S. Subramanian, L.-A. Ragnarsson, P. Weckx, B. Chehab, G. Hellings, J. Ryckaert, E. Dentoni Litta, and N. Horiguchi, 2021 IEEE Symposium on VLSI Technology, T 2.1 (2021).

- J. Zhang, J. Frougier, A. Greene, X. Miao, L. Yu, R. Vega, P. Montanini, C. Durfee, A. Gaul, S. Pancharatnam, C. Adams, H. Wu, H. Zhou, T. Shen, R. Xie, M. Sankarapandian, J. Wang, K. Watanabe, R. Bao, X. Liu, C. Park, H. Shobha, P. Joseph, D. Kong, A. Arceo De La Pena, J. Li, R. Conti, D. Dechene, N. Loubet, R. Chao, T. Yamashita, R. Robison, V. Basker, K. Zhao, D. Guo, B. Haran, R. Divakaruni, and H. Bu, *2019 IEEE International Electron Device Meeting (IEDM)*, 11.6.1. (2019).

- 4. A. Hikavyy, C. Porret, R. Loo, M. Mencarelli, P. Favia, M. Ayyad, B. Briggs, R. Langer, and N. Horiguchi, *ECS Trans.* **104** (4), 139 (2021).

- H. Mertens, R. Ritzenthaler, Y. Oniki, P. Puttarame Gowda, G. Mannaert, F. Sebaai, A. Hikavyy, E. Rosseel, E. Dupuy, A. Peter, K. Vandersmissen, D. Radisic, B. Briggs, D. Batuk, J. Geypen, G. Martinez-Alanis, F. Seidel, O. Richard, B.T. Chan, J. Mitard, E. Dentoni Litta, and N. Horiguchi, 2022 IEEE International Electron Device Meeting (IEDM), 23.1.1 (2022).

- P. Schuddinck, F. M. Bufler, Y. Xiang, A. Farokhnejad, G. Mirabelli, A. Vandooren, B. Chehab, A. Gupta, C. Roda Neve, G. Hellings and J. Ryckaert, 2022 IEEE Symposium on VLSI Technology, p. 365 (2022).

- S. Subramanian, M. Hosseini, T. Chiarella, S. Sarkar, P. Schuddinck, B.T. Chan, D. Radisic, G. Mannaert, A. Hikavyy, E. Rosseel, F. Sebaai, A. Peter, T. Hopf, P. Morin, S. Wang, K. Devriendt, D. Batuk, G. T. Martinez, A. Veloso, E. Dentoni Litta, S. Baudot, Y. K. Siew, X. Zhou, B. Briggs, E. Capogreco, J. Hung, , R. Koret, A. Spessot, J. Ryckaert, S. Demuynck, N. Horiguchi, and J. Boemmels, 2020 IEEE Symposium on VLSI Technology, TH3.1 (2020).

- A. Vandooren, N. Parihar, J. Franco, R. Loo, H. Arimura, R. Rodriguez, F. Sebaai, S. Iacovo, K. Vandersmissen, W. Li, G. Mannaert, D. Radisic, E. Rosseel, A. Hikavyy, A. Jourdain, O. Mourey, G. Gaudin, G. Besnard, C. Roda Neve, B.-Y.

Nguyen, I. Radu, E. Dentoni Litta, and N. Horiguchi. et al., 2022 IEEE Symposium on VLSI Technology, p. 330 (2022).

- N. Horiguchi, H. Mertens, T. Chiarella, S. Demuynck, V. Vega-Gonzalez, A. Vandooren, A. Veloso, M. Garcia Bardon, G. Sisto, A.Gupta, Z. Tokei, S. Biesemans, and J. Ryckaert, 2023 IEEE International Electron Device Meeting (IEDM), 29.1.1 (2023).

- M. Radosavljević, C.-Y. Huang, R. Galatage, M. F. Qayyum, J. A. Wiedemer, E. Clinton, D. Bennett, H. Ryu, N. K. Thomas, P. Morrow, T. Michaelos, R. Nahm, N. Briggs, A. Roy, C. C. Kuo, S. Atanasov, S. Ghose, N. Zussblatt, N. Kumar, D. Unluer, M. Beasley, J. M. Tan, L. H. Tan, M. Elkins, S. Cekli, R. Hermann, L. Shoer, M. Abd El Qader, U. Desai, T. Edwards, P. Prasad, J. Armstrong, M. Ghosh, Y.-A. Liao, V. Kapinus, D. Dixit, M. K. Harper, P. Tran, K. L. Cheong, A. Fatehi, A. A. Oni, N. Franco, B. J. Krist, M. V. Metz, G. Dewey, R. Schenker, and M. J. Kobrinsky, 2023 IEEE International Electron Device Meeting (IEDM), 29.2.1 (2023).

- 11. S. Liao, L. Yang, T.K. Chiu, W.X. You, T.Y. Wu, K.F. Yang, W.Y. Woon, W.D. Ho, Z.C. Lin, H. Y. Hung, J.C. Huang, S.T. Huang, M.C. Tsai, C.L. Yu, S.H. Chen, K.K. Hu, C.C. Shih, Y.T. Chen, C.Y. Liu, H.Y. Lin, C.T. Chung, L. Su, C.Y. Chou, Y.T. Shen, C.M. Chang, Y.T. Lin, M.Y. Lin, W.C. Lin, B.H. Chen, C.S. Hou, F. Lai, X. Chen, J. Wu, C.K. Lin, Y.K. Chen, H.T. Lin, Y.C. Ku, S.S. Lin, L.C. Lu, S.M. Jang, and M. Cao, 2023 IEEE International Electron Device Meeting (IEDM), 29.6.1 (2023).

- S. Demuynck, V. Vega Gonzalez, C. Toledo de Carvalho Cavalcante, L. P. B. Lima, K. Stiers, C. Sheng, A. Vandooren, M. Hosseini, D. Zhou, H. Mertens, T. Chiarella, J. Boemmels, R. Loo, E. Rosseel, C. Porret, Y. Shimura, A. Akula, G. Mannaert, S. Choudhury, V. Brissonneau, E. Dupuy, T. Sarkar, N. F. Vergel, A. Peter, N. Jourdan, J.-P. Soulie, K. Vandersmissen, F. Sebaai, P. P. Gowda, K. Lai, A. Mingardi, S. Sumar Sarkar, K. Dhave, BT Chan, A. Sepulveda Marquez, R. Langer, I. Gyo Koo, E. Altamirano Sanchez, K. Devriendt, P. Rincon Delgadillo, F. Lazzarino, J. Mitard, J. Geypen, E. Grieten, D. Batuk, Y.-F. Chen, F. Verbeek, F. Holsteyns, S. Subramanian, N. Horiguchi, and S. Biesemans, 2024 IEEE Symposium on VLSI Technology, T5.2 (2024).

- R. Loo, Y. Shimura, A. Akula, C. Porret, A. Merkulov, M. Ayyad, H. Han, O. Richard, A. Impagnatiello, and A. Hikavyy, 2023 International Conference on Solid State Devices and Materials (SSDM), p. 291 (paper F-5-03) (2023).

- 14. R. Loo, N. Gosset, M. Isaji, Y. I. Kawamura, A.Y. Hikavyy, E. Rosseel, C. Porret, A. Nalin Mehta, and J.-M. Girard, *ECS Trans.* **109** (4), 135 (2022).

- 15. Y. Muraki, Y. Oniki, P. P. Gowda, E. Altamirano-Sánchez, H. Mertens, N. Horiguchi, F. Holsteyns, S. Kal, C. Alix, K. Kumar, A. Mosden, T. Hurd, and N. Takahashi, Advanced Etch Technology and Process Integration for Nanopatterning XI, 12056-6 (2022).

- 16. Y. Oniki, K. Kenis, K. Wostyn, E. Altamirano-Sánchez, and F. Holsteyn, *Surface Preparation and Cleaning Conference (SPCC)*, (2020).

- 17. J. M. Hartmann, V. Destefanis, G. Rabillé, and S. Monfray, *Semicond. Sci. and Technol.* **25** (10), 105009 (2010).

- P. Raghavan, M. Garcia Bardon, D. Jang, P. Schuddinck, D.Yakimets, J. Ryckaert, A. Mercha, N. Horiguchi, N. Collaert, A. Mocuta, D. Mocuta, Z. Tokei, D. Verkest, A. Thean, and A. Steegen, 2015 Custom Integrated Circuits Conference (CICC), 1 (2015).

- C. Porret, J.-L. Everaert, M. Schaekers, L.-A. Ragnarsson, A. Hikavyy, E. Rosseel, G. Rengo1, R. Loo, R. Khazaka, M. Givens, X. Piao, S. Mertens, N. Heylen, H. Mertens, C. Toledo de Carvalho Cavalcante, G. Sterckx, S. Brus, A. Nalin Mehta, M. Korytov, D. Batuk, P. Favia, R. Langer, G. Pourtois, J. Swerts, E. Dentoni Litta, and N. Horiguchi, 2022 IEEE International Electron Device Meeting (IEDM), 34.1.1 (2022).

- 20. C. Porret, A. Hikavyy, E. Rosseel, P. Eyben, G. T. Martinez, J.-L. Everaert, G. Rengo, B. Pollefliet, Y. Shimura, R. Langer, N. Horiguchi, and R. Loo, 2023 *International Conference on Solid State Devices and Materials (SSDM)*, p. 287 (paper F-5-03) (2023).

- 21. F. Panciera, K. Hoummada, C. Perrin, M. El Kousseifi, R. Pantel, M. Descoins, M. Gregoire, M. Juhel, D. Mangelinck, *Microelectron. Eng.* **120**, 34 (2014).

- A. Veloso, A. Jourdain, D. Radisic, R. Chen, G. Arutchelvan, B. O'Sullivan, H. Arimura, M. Stucchi, A. De Keersgieter, M. Hosseini, T. Hopf, K. D'have, S. Wang, E. Dupuy, G. Mannaert, K. Vandersmissen, S. Iacovo, P. Marien, S. Choudhury, F. Schleicher, F. Sebaai, Y. Oniki, X. Zhou, A. Gupta, T. Schram, B. Briggs, C. Lorant, E. Rosseel, A. Hikavyy, R. Loo, J. Geypen, D. Batuk, G. T. Martinez, J. P. Soulie, K. Devriendt, B. T. Chan, S. Demuynck, G. Hiblot, G. Van der Plas, J. Ryckaert, G. Beyer, E. Dentoni Litta, E. Beyne, and N. Horiguchi, *IEEE Trans. Elec. Dev.* 69 (12), 7173 (2022).

- 23. A. Jourdain, F. Schleicher, J. De Vos, M. Stucchi, E. Chery, A. Miller, G. Beyer, G. Van der Plas, E. Walsby, K. Roberts, H. Ashraf, D. Thomas, and E. Beyne 2020 *IEEE 70<sup>th</sup> Electronic Components and Technology Conference (ECTC)*, 42 (2020).

- 24. R. Loo, A. Jourdain, G. Rengo, C. Porret, A. Hikavyy, M. Liebens, L. Becker, P. Storck, G. Beyer, and E. Beyne, *ECS J. Solid State Sci. Techn.* **10** (1), 014001 (2021).

- 25. A. Hikavyy, I. Zyulkov, H. Mertens, L. Witters, R. Loo, and N. Horiguchi, Mater. Sci. Semicond. Process. **70**, 24 (2017).

- 26. C. Porret, A. Hikavyy, J. F. Gomez Granados, S. Baudot, A. Vohra, B. Kunert, B. Douhard, J. Bogdanowicz, M. Schaekers, D. Kohen, J. Margetis, J. Tolle, L. P. B. Lima, A. Sammak, G. Scappucci, E. Rosseel, R. Langer, and R. Loo, *ECS J. Solid State Sci. Technol.* 8 (8), P392 (2019).

- 27. E. Rosseel, C. Porret, A. Hikavyy, R. Loo, M. Tirrito, B. Douhard, O. Richard, N. Horiguchi, and R. Khazaka, *ECS Trans.* **98** (5), 37 (2020).

- 28. E. Rosseel, C. Porret, A. Hikavyy, R. Loo, O. Richard, G. T. Martinez, D. Batuk, H. Mertens, E. Dentoni Litta, and N. Horiguchi, *ECS Trans.* **109** (4), 93 (2022).

- 29. E. Rosseel, C. Porret, T. Dursap, R. Loo, H. Mertens, J. Ganguly, R. Sarkar, C. Toledo de Carvalho Cavalcante, O. Richard, J. Geypen, B. Marozas, D. Casey, R. Khazaka, S. Demuynck, L. Petersen, R. Langer, S. Biesemans, and N. Horiguchi, *PRIME 2024, Symposium G03: SiGe, Ge & Related Compounds: Materials, Processing and Devices 11*, abstract no G03-2298 (accepted).

- 30. E. Rosseel, C. Porret, T. Dursap, R. Loo, H. Mertens, J. Ganguly, R. Sarkar, C. Toledo de Carvalho Cavalcante, O. Richard, J. Geypen, B. Marozas, D. Casey, R. Khazaka, S. Demuynck, L. Petersen, R. Langer, S. Biesemans, and N. Horiguchi, *ECS Trans. 2024* (submitted to the current proceedings volume).

- 31. D. Kohen, V. D'Costa, N. Bhargava, and J. Tolle, Semicond. Sci. Technol. 33 104003 (2018).

- 32. Z. Kong, Y. Song, H. Wang, X. Liu, X. Wang, J. Liu, B. Li, J. Su, X. Tan, Q. Luan, H. Lin, Y. Ren, Y. Zhang, J. Liu, J. Li, A. Du, H. H. Radamson, C. Zhao, T. Ye, and G. Wang, ACS Appl. Mater. Interfaces 15 (48), 56567 (2023).

- 33. J. Bogdanowicz, M. Saib, M. Beggiato, G. Lorusso, V. Brissonneau, E. Dupuy, R. Loo, Y. Shimura, A. Akula, H. Arimura, P.P. Gowda, BT Chan, D. Zhou, H. Mertens, L. P. B. Lima, N. Horiguchi, S. Biesemans, J. Hung, I. Turovets, S. Wei, P. Hönicke, R. Ciesielski, P. Leray, and A.-L. Charley, *PRIME* 2024, Symposium G03: SiGe, Ge & Related Compounds: Materials, Processing and Devices 11, abstract no. G03-2302 (accepted).

- 34. J. Bogdanowicz, A.-L. Charley, and P. Leray, *Proc. SPIE* 12496, *Metrology, Inspection, and Process Control XXXVII*, 1249617 (2023).

- 35. P. Favia, O. Richard, G. Eneman, H. Mertens, H. Arimura, E. Capogreco, A. Hikavyy, L. Witters, P. Kundu, R. Loo, E. Vancoille, and H. Bender, *Semicond. Sci. Technol.* 34, 124003 (2019).

- 36. R. Ciesielski, J. Bogdanowicz, R. Loo, Y. Shimura, A. Mani, C. Mitterbauer, M. Kolbe, and V. Soltwisch, Proc. SPIE 12955, Metrology, Inspection, and Process Control XXXVIII, 1295507 (2024).

- 37. J. Frascaroli, M. Tonini, S. Colombo, L. Livellara, L. Mariani, P. Targa, R. Fumagalli, V. Samu, M. Nagy, G. Molnár, Á. Horváth, Z. Bartal, Z. Kiss, T. Sipocz, and I. Mica, *IEEE Trans. Semicon. Manuf.* 35 (3), 540 (2022).

- J. Frascaroli, S. Colombo, R. Fumagalli, I. Mica, L. Livellara, V. Samu, and G. Molnár, *Phys. Status Solidi A* 219, 2200150 (2022).

- 39. R. Loo, A. Hikavyy, D. Wang, K. Yamamoto, T. Sipőcz, Á. Kerekes, A. Akula, and Y. Shimura, 2023 International Conference on Solid State Devices and Materials (SSDM), p. 525 (paper M-3-05) (2023).

- 40. G. Rengo, D. Casey, B. Marozas, N. Claessens, and R. Khazaka, *PRIME 2024, Symposium G03: SiGe, Ge & Related Compounds: Materials, Processing and Devices 11*, abstract no. G03-2300 (accepted).

- 41. W. Vandervorst, Appl. Surf. Sci. 255, 805 (2008).

- 42. O. Dyck, D.N. Leonard, L.F. Edge, C.A. Jackson, E.J. Pritchett, P.W. Deelman, J. D. Poplawsky, *Adv. Mater. Interfac.* **4**, 1700622 (2017).

- 43. G. Brémond, A. Souifi, T. Benyattou, and D. Dutartre, *Thin Solid Films* **222** (1-2), 60 (1992).

- 44. J. C. Sturm, H. Manoharan, L. C. Lenchyshyn, M. L. W. Thewalt, N. L. Rowell, J. P. Noel, and D. C. Houghton, *Phys. Rev. Lett.*, **66**, 1362 (1991).